## CONTENTS -----

| Basic Theory                        |  |

|-------------------------------------|--|

| Transistor Circuits 1               |  |

| Measuring Instrument                |  |

| Wow-flutter Meter                   |  |

| One Point Service Technique         |  |

| Diagnosing Optical Pickups 13       |  |

| Microcomputer Fundamentals 31       |  |

| New Products                        |  |

| PAL-VHS Home VCR (VH-600) Continued |  |

# **Basic Theory**

### **Transistor Circuits**

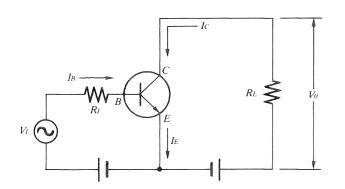

There are two types in transistors, NPN and PNP types as shown in Fig. 1. The NPN type is made of silicon. PNP transistors have been made of germanium. The germanium transistors, however, are being superseded by silicon transistors. A transistor has three main electrodes; emitter (E), base (B) and collector (C).

#### **1. Typical Transistor Circuits**

In wiring a transistor there are three main methods; common-emitter, common-base and common-collector wiring.

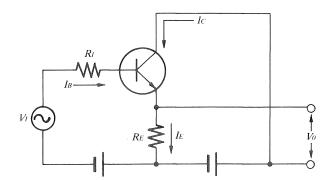

#### (a) Common-emitter Amplifier

In Fig. 2 the emitter element is common to both the input and output circuits. The amplification of this circuit is high. Its input impedance is medium and output impedance is high. This circuit is the most popular in amplifiers. It gives the following equations:

$I_E = I_C + I_B$   $h_{FE} = I_C/I_B$

h<sub>FE</sub>: DC current amplification with emitter grounded

The voltage amplification  $(A_V)$  is as follows:

$A_V = \frac{V_O}{V_I} = \frac{-R_L \cdot I_C}{R_I \cdot I_B} = -\frac{R_L \cdot h_{FE} \cdot I_B}{R_I \cdot I_B} = -\frac{R_L}{R_I} h_{FE}$ R<sub>1</sub>: Input impedance

R<sub>L</sub>: Load impedance

The voltage amplification can be known by dividing output impedance by input impedance and then multiplying the result by  $h_{FE}$ . The minus mark means that the input phase is inverted at the output.

Fig. 2 Common-emitter Amplifier

Fig. 1 Transistor Symbols

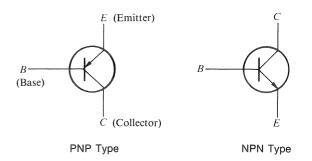

#### (b) Common-base Amplifier

The features of this circuit are low input impedance and high output impedance. The current amplification ( $h_{FB}$ ) of this circuit is:

$h_{FB} = (I_C/I_E) < 1$  $h_{FB}$ : DC amplification with base grounded

The voltage amplification (Av) is:

$$A_{V} = \frac{V_{O}}{V_{I}} = \frac{R_{L} \cdot I_{C}}{R_{I} \cdot I_{E}} = \frac{R_{L} \cdot h_{FB} \cdot I_{E}}{R_{I} \cdot I_{E}} = \frac{R_{L}}{R_{I}} h_{FB}$$

$R_L/R_I$  should be made large to increase the amplification because  $h_{FB}$  is less than 1. The input and output signals are inphase each other.

Fig. 3 Common-base Amplifier

#### (c) Common-collector Amplifier

This is also called emitter-follower. In this circuit current amplification is high, voltage amplification is less than 1, input impedance is high and output impedance is low. This is, therefore, used as a buffer.

*Buffer:* A circuit which converts impedance and isolates one electrical circuit from another to prevent undesirable interaction between two stages.

This gives the following equations.

$I_E = I_C + I_B = h_{FE} I_B + I_B = (1 + h_{FE}) I_B$

The input impedance ( $Z_I$ ) becomes nearly the multiplied value of  $R_E$  by  $h_{FE}$ :

$$Z_{I} = \frac{(1 + h_{FE}) I_{B} R_{E}}{I_{B}} \approx h_{FE} R_{E}$$

The output impedance (Z<sub>0</sub>) is:

$Z_{\rm O} \;=\; \frac{R_{\rm I} \; I_{\rm C}/(1+h_{\rm FE})}{I_{\rm C}} \; \rightleftharpoons \; \frac{R_{\rm I}}{h_{\rm FE}}$

$A_v$  is nearly equal to 1 because  $R_E$  is generally much larger than  $R_I$ . The output phase is the same as input phase.

$$A_{V} = \frac{V_{O}}{V_{I}} = \frac{R_{E}I_{B}(1+h_{FE})}{R_{I}+R_{E}I_{B}(1+h_{FE})}$$

$$= \frac{R_{E}(1+h_{FE})}{R_{I}+R_{E}(1+h_{FE})} \rightleftharpoons 1$$

Fig. 4 Common-collector Amplifier

| Table 1 | Typical | Transistor | Amplifiers |

|---------|---------|------------|------------|

|---------|---------|------------|------------|

| Amplifiers               | Common-<br>emitter amp. | Common-<br>collector amp. | Common-base<br>amp. |

|--------------------------|-------------------------|---------------------------|---------------------|

| Input impedance          | Medium<br>(1.95k)       | High (300k)               | Low (13)            |

| Output<br>impedance      | High (1k)               | Low (19.7)                | High (1k)           |

| Voltage<br>amplification | - 75.6                  | 1                         | 75.6                |

| Current amplification    | - 150                   | 150                       | 1                   |

| Usage                    | Signal                  | Buffer                    | Buffer              |

#### 2. Biasing

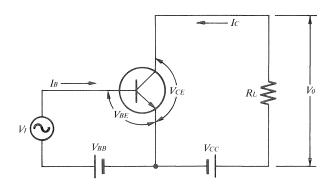

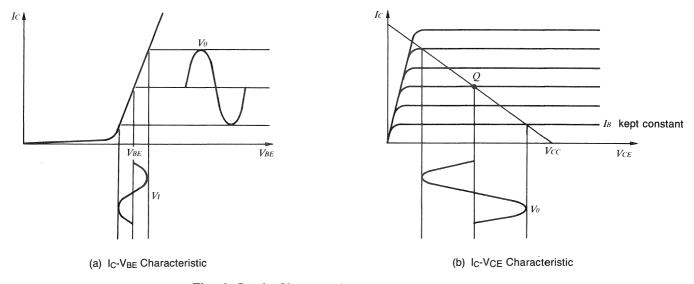

To operate a transistor, a DC voltage should be applied between the base and emitter in addition to the collector and emitter as shown in Fig. 5. The voltage between the base and emitter ( $V_{BE}$ ) is called "bias voltage". The collector current flows when  $V_{BE}$  exceeds approximately 0.6V in silicon transistors (0.2V in gelmanium transistors).

$$V_{CE} = V_{CC} - I_C R_L$$

Fig. 5 Basic Bias Circuit

The above equation gives a straight line on the family of collector characteristic curves as shown in Fig. 6 (b). The operating point or quiescent point "Q" of the transistor moves on the straight line as the collector current  $(I_C)$  varies. This line is called a "load line" because the slope of the line depends on collector load resistance. To make the amplitude of the output signal maximum the operating point should be at the center of the load line by setting the  $V_{CE}$  at  $V_{CC}/2$ . The I<sub>C</sub> varies greatly even when the  $V_{BE}$  varies just a little. This characteristic is employed for signal amplification.

Fig. 6 Static Characteristic of a Transistor

#### 3. Bias Circuit

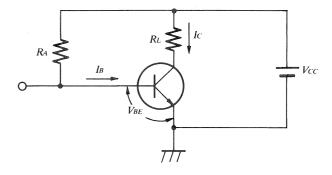

#### (a) Fixed bias circuit

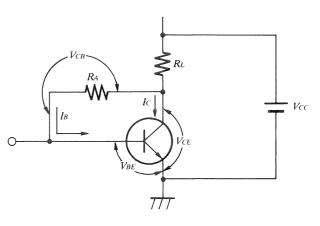

This circuit supplies a base current through a fixed R<sub>A</sub>. Its operation highly depends on temperature. When the transistor temperature increases, the operating point "Q" moves leftward making the dissipation in the transistor increase rapidly and causing distortion and thermal runaway. The dissipation increases the temperature in a vicious circle. Dissipation is the loss of electrical energy as heat. This circuit, however, is simple and consumes small power.

Fig. 7 Fixed Bias Circuit

Fig. 8 Self-bias Circuit

#### (b) Self-bias (automatic) circuit

In this circuit  $R_L$  prevents  $I_C$  from increasing excessively. When  $I_C$  increases, the voltage across the  $R_L$  increases,  $V_{CE}$ ,  $V_{CB}$  and  $I_B$  decrease. Then  $I_C$  decreases. Thus the operation of the amplifier is stabilized.

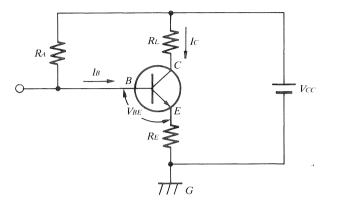

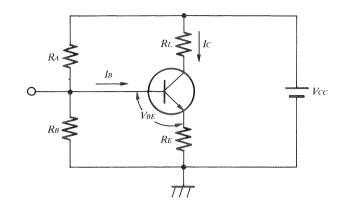

#### (c) Current-feedback bias circuit

In Fig. 9  $R_E$  stabilizes  $I_C$ . When the temperature and  $I_C$  increases, the emitter voltage increases because  $V_E$  is equal to ( $R_E \times I_C$ ). The  $V_{BE}$  decreases, then  $I_C$  decreases.

Fig. 9 Current-feedback Bias Circuit

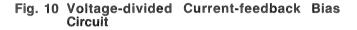

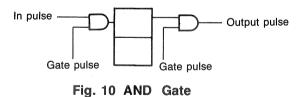

The circuit of Fig. 10 provides a stable bias voltage and low input impedance by dividing the power supply voltage with  $R_A$  and  $R_B$ .

#### 4. Basic Transistor Circuit

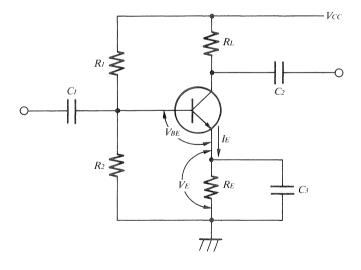

#### (a) 1-stage amplifier

Fig. 11 shows a 1-stage amplifier with a current feedback bias circuit. C1 and C2 are coupling capacitors. They pass AC signal blocking DC to avoid a circuit from affecting adjacent circuit.  $R_E$  stabilizes the  $I_C$  as discussed in (c). With the  $R_E$  the circuit composes an NFB loop for the AC input signal and decreases voltage amplification. The bypass capacitor C3 added parallelly to  $R_E$  works to minimize the NFB effect against AC and to maintain AC voltage amplification.

4

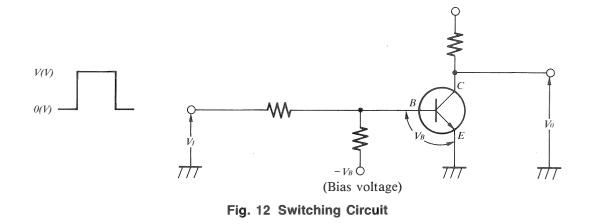

#### (b) Switching circuit

In Fig. 12 a transistor works as a switch. To cut off the transistor completely  $-V_B$  is applied to the base. With a pulsive signal applied to the input,  $V_B$  is negative and the

transistor is off while  $V_I$  is 0V, and the base current flows and the transistor goes ON when the input level becomes V volt. This circuit is popularly used in muting circuits.

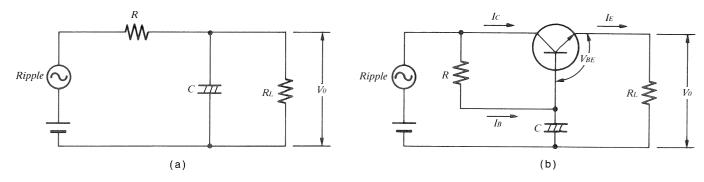

#### (c) Ripple filter

Ripple is the fluctuating portion of the DC output voltage of electronic converters such as rectifier in power supply circuit. The frequency is equal to that of the input or internally generated switching frequency. If a power supply voltage is applied to an equipment without smoothing the ripple, it will cause humming. The R and C in the circuit of Fig. 13 (a) filter the ripple on the DC. The higher the resistance and capacitance of the R and C, the better for smoothing the ripple. However, the resistance can not be made large because a large R decreases output voltage. In Fig. (b) a transistor solves the problem. The  $I_B$  becomes  $1/(1 + h_{FE})$  of the load current. This means that the R can be made large without decreasing  $V_O$ .

The relation between the currents in Fig. (b) is:

$I_E = I_B + I_C = I_B + I_B h_{FE} = I_B (1 + h_{FE})$

$$I_{\rm B} = I_{\rm E}/(1+h_{\rm FE})$$

Fig. 13 Ripple Filter

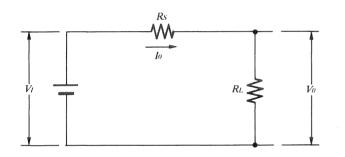

#### (d) Voltage regulator

Voltage regulator holds its output voltage at a nearly predetermined value regardless of the changes of normal input-voltage or output load impedance. This is employed in power supply circuit to stabilize output voltage because the ability of the ripple filter is not effective enough.

Fig. 14 shows the equivalent circuit to the simplest power supply circuit with a power source and load connected. Here the output voltage  $(V_0)$  can be obtained by:

$V_{O} = V_{I} - I_{O}R_{S}$

- V<sub>I</sub>: Input voltage

- Io: Load current

- R<sub>L</sub>: Load resistance

- R<sub>S</sub>: Internal resistance of power source

$I_{\rm O}$  varies depending on the input voltage and load impedance and affects the output voltage.

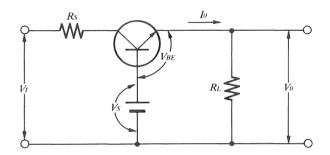

Fig. 14 Equivalent Circuit to the Power Supply Circuit

The circuit of Fig. 15 maintains the V<sub>O</sub> by varying I<sub>O</sub> with the help of a stabilizing transistor. When V<sub>O</sub> decreases, V<sub>BE</sub> decrease because V<sub>S</sub> is constant, then I<sub>O</sub> decreases and thus V<sub>O</sub> decreases to a predetermined level.

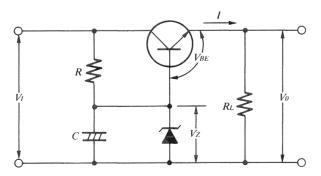

Fig. 16 shows a typical voltage regulator circuit. The battery (V<sub>S</sub>) has been superseded by a zener diode which prevents the base voltage from increasing above 0.7V. When V<sub>I</sub> fluctuates, the ripple component in the input current flows in the zener diode and does not affect the output. This circuit is a common-collector circuit. The output impedance of this circuit is low and the effect of the load current fluctuation to the output voltage is kept low. The output voltage is:

$$V_{\rm O} = V_Z - V_{\rm BE}$$

Fig. 15 Voltage Regulator With a Battery

Fig. 16 Voltage Regulator With a Zener Diode

# **Measuring Instrument**

### **Wow-flutter Meter**

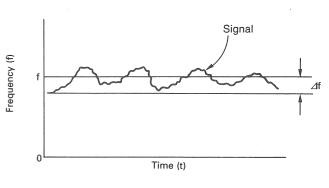

We sometimes experience that the sound on a tape or disc trembles or varies like that of the old movies. It is a kind of modulated distortion or frequency deviation produced by irregular motion of the driving mechanism of a turntable or tape transport during recording or reproduction. This is called "wow and flutter". The problem has almost been solved by a phase-locked loop servo system which converts speed error signal to a corrective voltage. Here we will discuss Wow Flutter Meter basing on MEGURO MK-668E.

#### 1. Definition

IEC-1969 (International Electro-technical Commission) defines the wow and flutter as follows:

Flutter: Unwanted frequency modulation or deviations of signals of 10Hz or above produced by irregular motion of a recording medium during recording or reproduction

Wow: Unwanted frequency modulation or deviations of signals in the range of 0.1Hz - 10Hz produced by irregular motion of a recording medium during recording or reproduction

Drift: Slow and random speed variation of a recording medium close to 0Hz

Wow and flutter is expressed by the percentage of the frequency deviation to the input frequency as follows:

Wow and flutter =

$$\frac{\Delta f}{f} \times 100$$

[%]

f : Input frequency

$\Delta f$ : Frequency deviation

100

The above relation can be converted to voltage relation by a frequency discriminator:

Wow-and-flutter:

$$\frac{\Delta V}{V} \ge 100$$

[%]

V : F-V converted DC voltage

$\triangle V$ : F-V converted AC voltage of wow and flutter component

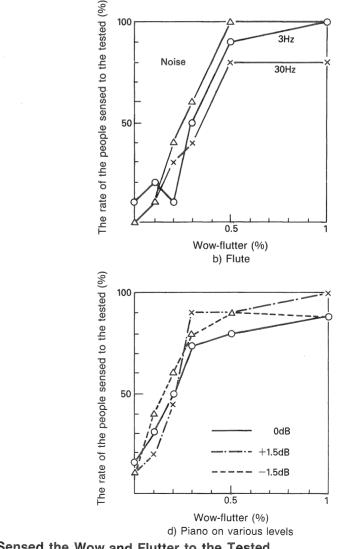

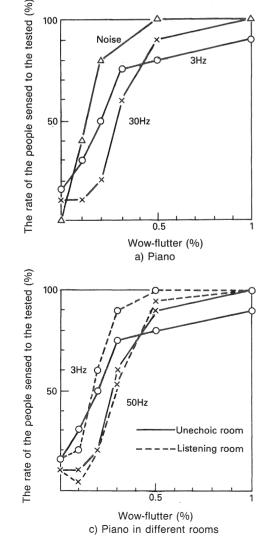

The sensitivity of our ears differs individually and depends on the conditions such as the materials, size and shape of listening room (live or dead), sound quality and level. Fig. 2 shows the percentage of the people sensed the wow and flutter under various conditions. (a) indicates that 50% of the people tested sensed the wow of 0.2% on the 3Hz signal. It is strange that some people feel wow and flutter even when it is 0%.

Fig. 2 The Rate of the People Sensed the Wow and Flutter to the Tested

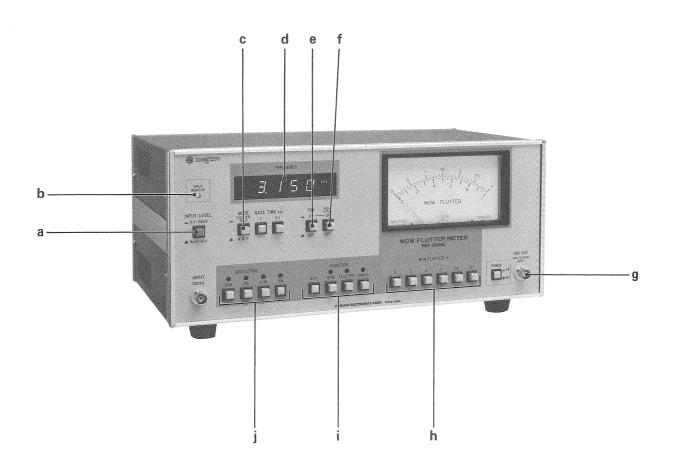

#### 2. Panel Descriptions

**a. INPUT LEVEL** Input level range is selectable between 0.1V-30mV and 5mV-10V.

**b. INPUT MONITOR** When the input level is high enough, the LED lights.

**c. MODE** Selects wow and flutter meter or frequency counter.

**d. FREQUENCY** Input signal frequency counter. This can count from 0.001kHz to 9.999kHz or from 0.01kHz to 99.99kHz with the GATE TIME set at 1 sec or 0.1 sec respectively and is useful as an independent frequency counter.

**e. FIM** Frequency intermodulation can be measured with this button depressed.

**f. 160Hz HPF** Depress this to eliminate wow and flutter component when measuring FIM.

g. OSC OUT Standard signal is available here. 3kHz signal for NAB, JIS and CCIR and 3.15kHz for DIN.

h. WOW FLUTTER % Six ranges are selectable.

**i.** FUNCTION

WTD To weight\* input signal.

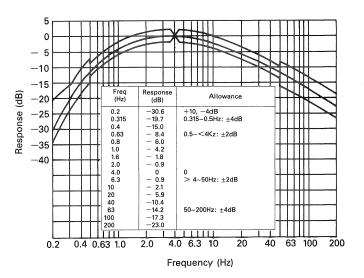

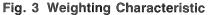

\*Weighting: The artificial adjustment of measurements in frequency characteristic to meet the sensitivity of the human ears. In 1956 CCIR adopted the DIN's weighting standard as an international standard. Since then many nations and associations such as IEC, JIS, NAB have adopted the weighting curve as their standard. Fig. 3 shows the curve.

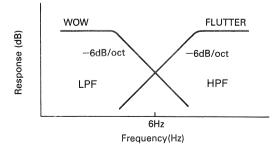

| WOW     | To measure wow only $(0.5 - 6Hz)$             |

|---------|-----------------------------------------------|

| FLUTTER | To measure flutter only $(6 - 200 \text{Hz})$ |

| UNWTD   | To measure wow and flutter without            |

|         | weighting                                     |

**j. INDICATION** The reading depends on the standard selected from NAB, JIS, CCIR and DIN.

- CCIR: International Radio Consultative Committee

- DIN: Deutche Industrie Normen

- IEC: Internation Electrotechnical Commission

- JIS: Japanese Industrial Standard

- NAB: National Association of Broadcasters

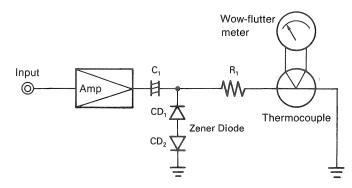

There are three main ways of indication; rms rectification — rms (root-means-square) indication by the JIS, mean-value rectification — rms indication by the NAB, and peak-value rectification — peak-to-peak (p-p) indication by the DIN. The DIN is widely adopted by many European CCIR member countries. Japan has recently adopted the DIN. They are different each other. Let's see the typical circuits.

*RMS indication*: Fig. 4 shows popular rectifiers which operate with a time constant made by  $C_1$  and  $R_1$ . Unlike a thermocouple, RC rms circuit has many advantages such as linear scale and wide selection of meters in dynamic characteristic. In the characteristic, the JIS requires lenient indication of  $100 \pm 5\%$  with the input pulses of 5-second width.

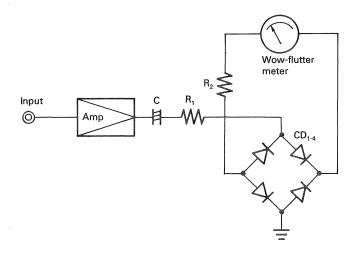

Fig.4 RMS-indication Circuit

*Mean-value rectification*: The full-wave rectifier shown in Fig. 5 gives mean value. The NAB requires to employ a VU meter. Reading the VU meter is very hard because its pointer moves very quickly.

Fig. 5 Mean-value Rectification Circuit

(a) Charging Time

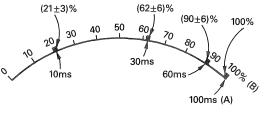

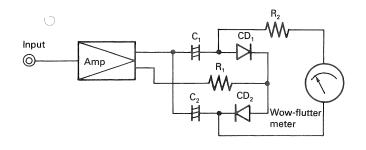

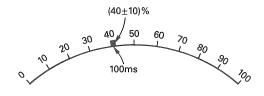

*p-p-value indication*: The circuit of Fig. 6 employs a voltage doubler to indicate p-p value. The DIN strictly prescribes the dynamic characteristic of peak indication circuit. Fig. 7 shows its characteristics. The pointer should swing up to the full scale in 100ms when a large pulse is applied and return to the 40% point in 100ms after the pulse disappears.

(b) Discharging Time

Fig. 7 Dynamic Characteristics of p-p Indication

#### k. TO SCOPE (rear panel)

The waveform of the wow and flutter signal is observable on an oscilloscope taking its signal from this terminal. I. TO RECORDER

Frequency demodulated signal is available here.

#### 3. Principle

A wow meter has the same frequency demodulator as those of FM tuners because the wow and flutter are FM signals. A 3kHz standard signal recorded on a test disc or tape is reproduced. The 3kHz signal will be FMed and AMed in the turntable or deck to be measured. Its output is applied to the wow meter.

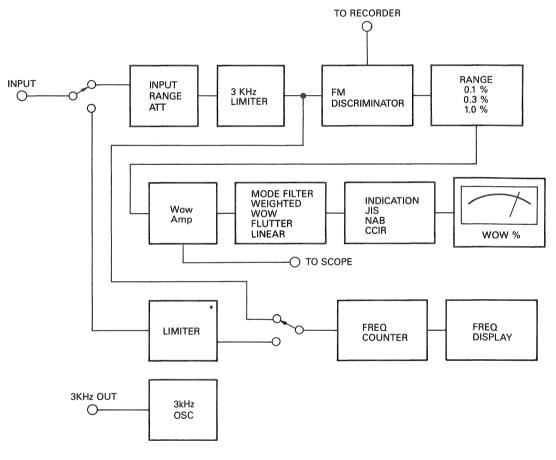

In the meter the signal level is adjusted and its amplitude is limited to eliminate the effect of AM component. Wow-and-flutter component is taken out of the limited signal by a 3kHz frequency discriminator. The wow-andflutter signal is attenuated to meet the selected meter range. It is amplified and is weighted in accordance with the standard selected from NAB, JIS, CCIR and DIN. Wow and flutter can be separately taken out by a 6Hz LPF or HPF. Fig. 9 shows their characteristics. The signal is rectified and indicated as specified by the respective standard selected. The current models can measure tape speed and motor's revolution with a built-in frequency counter.

Fig. 8 Block Diagram of Wow Meter

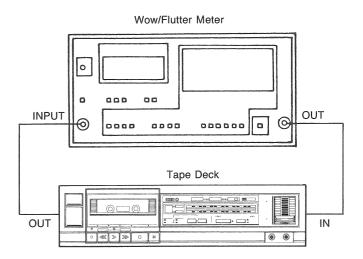

#### 4. Measuring a Tapedeck

#### *Measurement with a test tape by the JIS (different recorder/player):*

The JIS measurement uses a test tape with a 3kHz signal recorded by a standard recorder. In this way the tape is played on a tape deck other than the one recorded. A test tape is played on the unit to be tested, the output of the unit is weighted by the JIS, measured and displayed in rms percentage on the meter as shown in Fig. 10. The test tape should be on a reel of the largest type installable and the test should be made at the beginning, midway and the end for at least 10 seconds at each point, and the largest value among the three should be taken. Many deck manufacturers follow this way.

#### Simultaneous recording/playback:

In case the total value throughout recording and reproduction is required, a 3kHz signal is recorded on a tape, it is rewound and then reproduced on the same unit to be tested. The measurement is repeated several times, and the worst value except those measured when starting is taken. In this way accurate measurement will be difficult because particular frequency components determined by head gap and the wave length of flutter signal will be emphasized or suppressed.  $\nearrow$

#### Nonsimultaneous recording/playback:

In this way the measured value may vary from time to time due to the signal phase difference between recording and reproduction. DIN employs this method. The meter pointer will not become stable because the wow-flutter signal contains various frequency components.

Electro-mechanic Testing Association stipulates it as the maximum reading within 20 seconds.

Fig. 10 Wiring Diagram for Measuring a Tape Deck

## 5. Simplified Calibration of Wow Meter With a Tape

Rough calibration of the meter can be made with a test disc or tape recorded with a 3kHz signal added with the standard 3% wow-and-flutter signal. They are available on the market. A test tape can be made by recording the signal from the disc to a tape. The turntable and tape deck should be high in performance. The distortion of the deck should be less than 0.1%. The distortion of less than 0.1% added by the deck is negligible.

Play the disc or tape on the high-performance deck, apply the 3kHz signal that includes the wow-flutter signal to the INPUT of the wow meter to be calibrated and turn the screws in the holes above the INDICATION and FUNCTION knobs as indicated in the instruction manual attached to the meter. Remove the screwdriver when the meter indicates 3% distortion.

# **One Point Service Technique**

### **Diagnosing Optical Pickups**

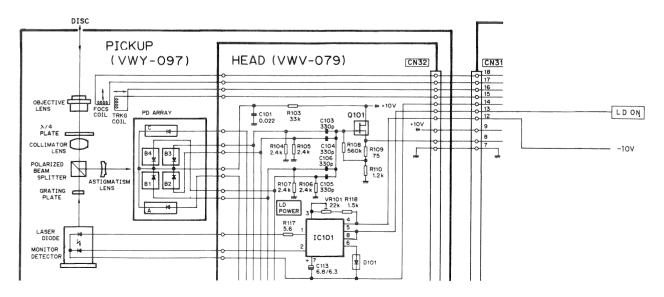

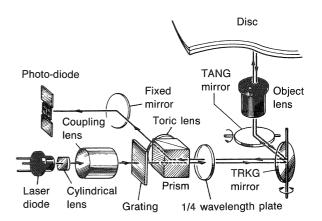

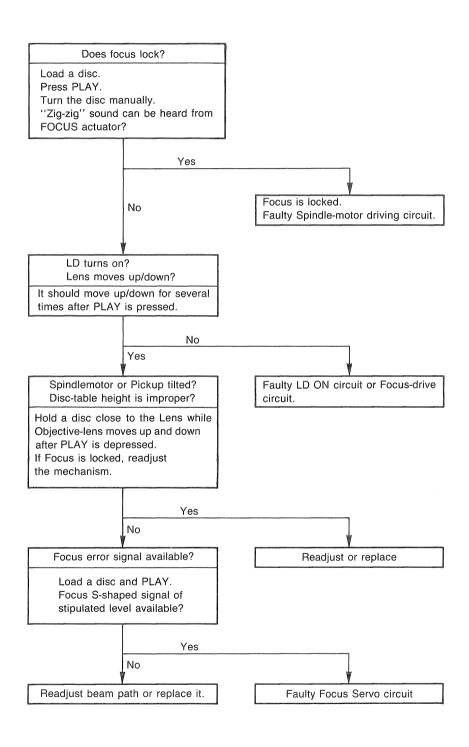

High precision is required in adjusting the Pickup of LD and CD players after replacing it or Spindle-motor because laser beam should be converged to  $\phi 1.5\mu$ m to read pits of  $\phi 0.5\mu$ m. Here we will discuss the ways to find which component is faulty, Pickup or mechanical component, and to see if they are properly adjusted.

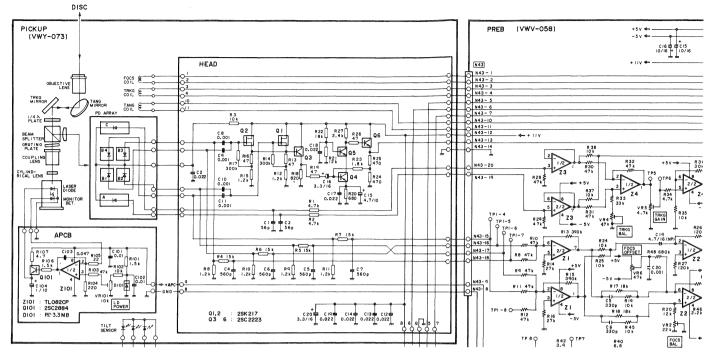

#### 1. Optical Pickup

The trouble of Pickup is caused by beam path deviation which prevents the beam reflected on the disc from reaching the center of the Photo Detector or by faulty components inside the Pickup. Faulty Pickups should be replaced because replacing the components inside the Pickup is possible only in our factory. Care should be taken in judging a Pickup to be faulty because it costs very much.

#### 2. Pickup Problems

The symptoms of the disorder of Pickup are:

- a. Laser diode does not turn on.

- b. Lens does not move up and down when starting.

- c. FOCUS Servo does not lock.

- d. SPINDLE Servo does not lock.

- e. Beam skips tracks.

- f. SEARCH is inoperative.

- g. Picture is noisy.

Photo 1 Optical Pickup

Let us troubleshoot them.

#### a. Laser diode does not turn on.

*Check point:* Are APC (Automatic Power Control) current and LD ON signal applied to Pickup?

Yes: Replace Pickup because the trouble is in Laser Diode or APCB in Pickup.

Fig. 1 Circuit of Pickup

*No:* Faulty power supply block. The following conditions should be satisfied to apply LD ON signal to Pickup. Verify them.

| LD-1100 series:        | INTER-LOCK Switch: ON          |

|------------------------|--------------------------------|

|                        | LID-OPEN Sw: ON                |

| LD-700, CLD-900, etc.: | Disc Sensor, which also senses |

|                        | 8"/12" disc size, operates.    |

| LD-707, CLD-909, etc.: | Disc Sensor, which also senses |

|                        | TILT, operates.                |

|                        | Door Sw is closed.             |

| P-D70 series           | INTER-LOCK Sw: ON.             |

| PD-5010, 5030 series   | CLAMP Sw: ON.                  |

|                        |                                |

#### b. Objective-lens does not move up and down.

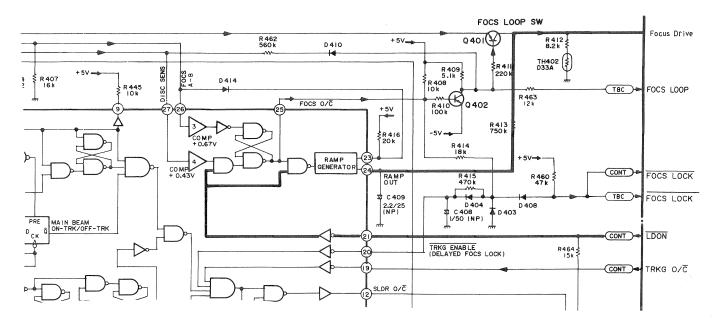

*Check point:* Is RAMP-generator working and a Drivecurrent applied to Focus-coil?

Yes: Shorted or opened Focus-coil, or sticking Lens.

No: Faulty RAMP-generator circuit

#### Note: Ramp Generator

Focus-Servo circuit works only when it receives Focus-Error signal from Pickup. Ramp-Generator generates a voltage to move Objective-lens up and down into the height range where focus lock is possible. This is activated when LD ON signal is applied, stops when Focus-Error signal is applied and then activates Focus Servo. If Focus-Error signal is unavailable, this circuit will stop generating Ramp signal in a few seconds and give up focusing. The player goes into STANDBY mode or EJECT mode.

Fig. 3 The Route of LDON Signal of LD-700

### c. Lens moves up and down, but does not focus-lock.

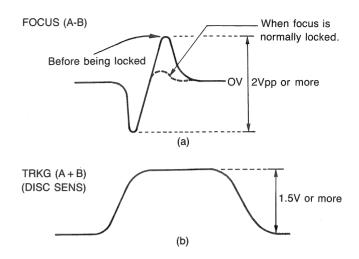

Check point: Observe the levels of FOCUS (A - B) and TRKG (A + B) signals on an oscilloscope while Lens is moving up and down.

If the Pickup is normal, an S-shaped wave shown in Fig. 4 (a) can be observed. The wave should be symmetrical and large in amplitude. If the wave is unsymmetrical and less than 2Vp-p, the beam axis must be deviated.  $\rightarrow$  Replace it.

With a normal Pickup, the focus locks only when the amplitude of TRKG (A + B) signal is more than 1.5 Vp-p and the voltage shifts from negative to positive.

Fig. 4 Focus and Tracking Signals

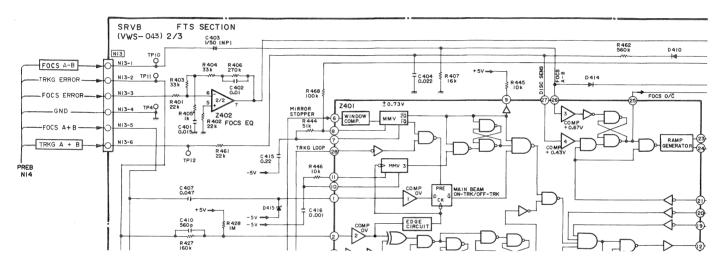

Fig. 5 The Signal Route of FOCUS A-B and TRKG A + B Signals (LD-700)

#### 3. Checking Optical Axis (Beam path)

#### **Requisites to good Pickup**

**a.** Pickup should be capable of producing a tracking error signal with a clear and flat envelope of high amplitude when the tracking loop is opened. (More than 7Vp-p at the Frame #20000 of a test disc of F1 — F5 played on CLD-900)

**b.** The reflected beam should shoot Photo-detector in the center.

c. The beam should converge to  $\phi 1.5 \mu m$  on the disc when Focus Servo locks.

d. The beam passing Objective-lens should be round.

If all of the above are satisfied and the trouble still exists, the cause of the trouble must be in other block than Pickup.

Checking methods of Pickup are as follows.

d. - g) Refer to the following.

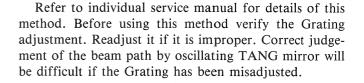

#### 3-1 Grating adjustment

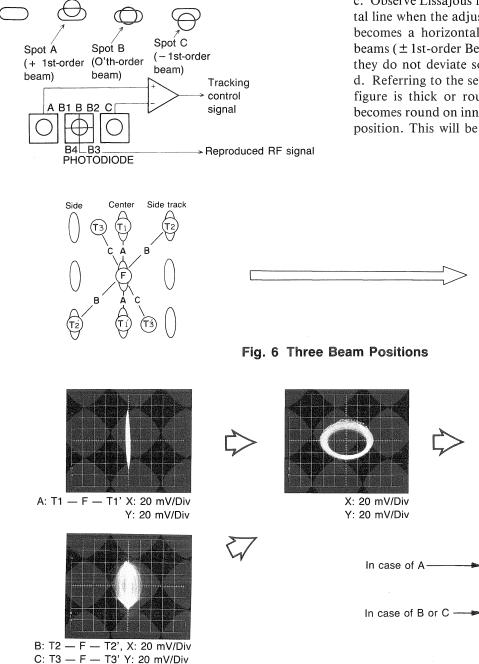

The Grating splits one beam coming from Laser Diode into three; the 0'th-order beam is for reading RF signal on a track and for generating Focus-error signal, and the  $\pm$ 1st-order beams are for tracking both sides of the track to keep the center beam trace the track center. Grating adjustment lets the three beams shoot a track as shown in Fig. 6. If this adjustment is improper, Tracking Servo will become impossible and the beam will skip tracks or the player will not play.

#### **Checking Grating Adjustment**

a. Apply TRKG (A - B) and TRKG (A + B) to X and Y channels of the oscilloscope respectively. Select X-Y mode. b. Play a test disc. Open TRKG SERVO at the frame shown below.

| Model          | Frame Number |

|----------------|--------------|

| LD-1100 series | 18,000       |

| LD-7000 series | 15,000       |

| CD             | Midway       |

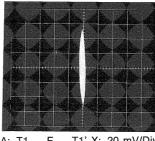

c. Observe Lissajous figures. The figure will be a horizontal line when the adjustment is optimum. The figure also becomes a horizontal line even when the two tracking beams ( $\pm$ 1st-order Beams) are on the side tracks. Usually they do not deviate so much.

d. Referring to the service manual, adjust it finely if the figure is thick or round in the vertical direction. If it becomes round on inner or outer tracks, adjust the motor position. This will be discussed later.

X: 20 mV/Div

Y: 20 mV/Div

5 mS/Div 100 mV/Div

Tracking Error Waveform

#### 3-2 Checking Beam Path (LD Player only)

#### a. PD Chopper

This is for verifying on an oscilloscope that the 0th-order beam is shooting the 4-segment photo detector in the center by comparing the levels of the signals taken from the four segments.

#### Note: PD Chopper (GGV-083)

PD chopper is the jig to adjust the photo detector's position properly. This jig was designed for the LD-1100 series models originally, however, it can be used for adjusting LD-700 and CLD-900.

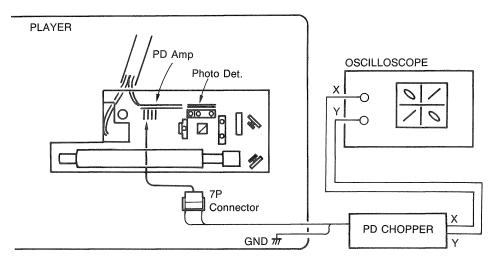

(1) Connect PD Chopper, oscilloscope and Player as illustrated below.

Photo 3 PD Chopper

Fig. 7 Connecting Diagram of LD-1100 or LD-660

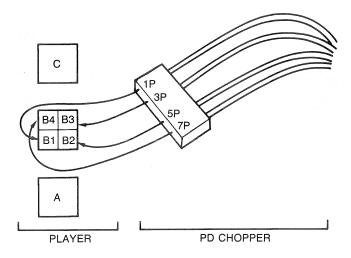

The PD chopper requires an adaptor to be connected when adjusting other players than LD-1100 series. It is connected to the Photo-Detector-output terminals B1 - B4.

If you have no adaptor, connect as below. The B1 - B4 of other models can be found easily on the circuit diagram.

Fig. 8 Connecting Pins with Photo Segments

Fig. 9 Pickup Circuit of LD-700

| Chopper's Terminal | PREB  |

|--------------------|-------|

| Pin 1              | TP1-5 |

| (B1)               |       |

| ·· 3               | TP1-7 |

| (B3)<br>'' 5       |       |

| ·· 5               | TP1-6 |

| (B2)               |       |

| ·· 7               | TP1-4 |

| (B4)               |       |

The Jig number of the adaptor for LD-700 and CLD-900 is GGF-057.

(2) Turn on the power of Player, PD chopper and oscilloscope.

(3) Select X-Y and DC input modes of oscilloscope.

(4) Move the beam spot to the center of the screen turning the POSITIONS.

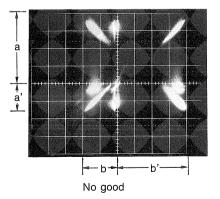

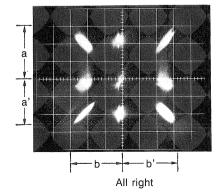

If a:a' or b:b' can not be made smaller than 3:2 or 2:3, the Pickup may be faulty.

(5) Play a test disc. Open the Tracking Servo in the midway on the disc.

(6) Observe waveform.

(7) If the beam path is deviated,

LD-1100 & -660: Adjust them with PD Adjusting Screw. LD-700& CLD-900: The Pickup can be adjusted separately with the following jigs.

| Mirror Jig        | GGF-056 |

|-------------------|---------|

| Adaptor Cord      | GGF-057 |

| PD Chopper Jig    | GGV-083 |

| 1.27mm Hex Wrench | GGF-060 |

Deviated Pickups mounted on the models other than the above should be replaced.

If the Lissajous figures are symmetrical across the center point, the Pickup is good. a = a', b = b'.

(b)

Photo 4

#### b. Mirror Biasing

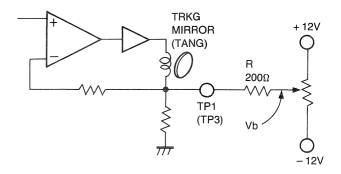

Beam path can be checked on the players which have TRKG and TANG mirrors such as LD-1100, LD-700 and CLD-900 by applying a bias current to the mirrors and making them oscillate.

The waveform of the Tracking Error signal tells us whether the beam path is shooting the mirrors' centers. It also tells us if the Mirror Actuator is worn out.

TRACKING MIRROR I

Photo 5 Tracking Mirror and Tangential Mirror

Fig. 10 Beam Path

#### c. Checking LD-700

#### PICKUP OPTICAL AXIS CHECK

Always perform this procedure after replacing the pickup and when it is suspected that the pickup has been deviated.

- Play a disc at around the track number 15,000.

- Open the TRKG loop. (Connect SRVB, Z401, PM4001 pins 20 and 22 with shorting clips.)

- Open the TANG loop. (Connect SRVB TP7 to ground.)

#### VERIFYING OPTICAL AXIS IN TRACKING DIRECTION

- Connect the bias-voltage output terminal of the opticalaxis-checking-jig (the current setting resistor should be set to 200 ohms) to TP1 (TRKG RTN) of SRVB.

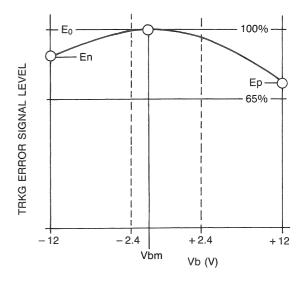

- Measure the TRKG error level at TP5 of PREB. Adjust the mirror bias VR of the jig so that the error level is maximized and then measure the peak-to-peak value  $E_0$  and the voltage Vbm being applied.

- Next, rotate the mirror bias VR all the way to the +12V side and measure the TRKG error p-p value, Ep. Then rotate the mirror bias VR all the way to the -12 V side and measure the TRKG error p-p value, En.

- If Vbm is within the range of  $\pm 2.4$ V: Ep > 0.63E<sub>0</sub> and En > 0.63E<sub>0</sub>

- If Vbm is outside the range of  $\pm 2.4$ V: Ep > 0.70E<sub>0</sub> and En > 0.70 E<sub>0</sub>

- If the above conditions are not satisfied replace the pickup.

Fig. 11 Tracking Adjustment

#### VERIFYING OPTICAL AXIS IN TANG DIRECTION

- Connect the bias-voltage output terminal of the opticalaxis checking jig to TP3 (TANG RTN) of SRVB.

- Measure the TRKG error level at TP5 of PREB. Adjust the mirror bias VR of the jig so that the error level is maximized and then measure the peak-to-peak value  $E_0$  and the voltage Vbm being applied.

- Rotate the mirror bias VR all the way to the +12 side and measure the TRKG error p-p value, Ep. Then rotate the mirror bias VR all the way to the -12V side and measure the TRKG error p-p value, En.

- If Vbm is within the range of  $\pm 2.4$ V: Ep > 0.63E<sub>0</sub> and En > 0.63E<sub>0</sub>

- If Vbm is outside the range of  $\pm 2.4$ V: Ep > 0.70E<sub>0</sub> and En > 0.70E<sub>0</sub>

- If the above conditions are not satisfied, replace the pickup.

#### Good Pickups satisfy the following conditions:

(1) TRKG Error voltage becomes maximum when bias voltage decreases to 0V. — The beam is shooting the center of the mirror.

(2) The amplitude of the TRKG error signal is stable when a bias is applied to the mirror to turn it. — The mirror will deflect larger than the above and the tracking error level will decrease if the mirror's actuator is worn out. In other words, if the beam is not shooting the mirror center, the deflection of the mirror will be abnormal and the error voltage will decrease.

The following jigs are for checking the path easily.

- \* Optical Axis Check Jig (GGF-058) for LD-700 and CLD-900)

- \* VSOP Adj Box (GGV-112) and Harness GGV-111 for LD-1100 and -660

The VSOP Adj. Box can also be used to check the path of LD-700 and CLD-900 when a special connector is adopted. Their operating instructions have simplified descriptions of the above checking method. But VSOP adj. Box is no longer available.

Fig. 12 Tracking Error Signal Level to Bias Voltage Vb

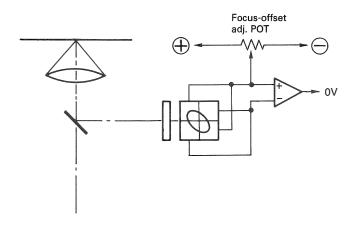

#### 3-3 FOCUS OFFSET

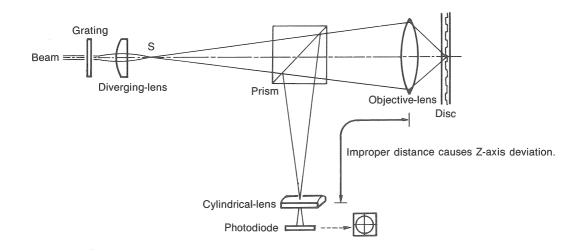

The above two methods are to verify that the reflected beam shoots the center of the Photo Diode. It is adjusted on X and Y axes in Fig. 13.

In adjusting Pickup, Z axis in addition to the X and Y axes should be imagined. The beam should be focused on the signal surface to read the pits. If the Objective-lens is off the right position, the beam will be beyond the control of FOCUS SERVO.

Х

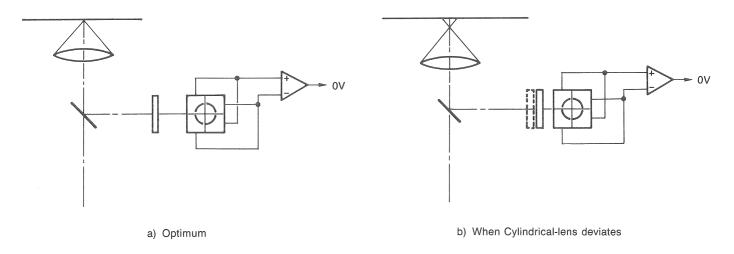

#### a. Cylindrical-lens and Focus Servo

The laser beam reflected from the disc is round in section. The beam is deformed by the Cylindrical-Lens to make an oblique spot on the Photo-Diode (PD) when the beam is out of focus. This time the average distance between the Objective-lens and Cylindrical-lens becomes shorter or longer than the optimum, and the Focus Servo system can not keep the beam focused on the pitted signal surface.

When the distance between the Objective-lens and Cylindrical-lens is optimum: The FOCUS SERVO circuit moves the Objective-lens and decreases the Focus Error signal level down to 0V to keep the beam focused on the signal surface of the disc. When it is improper: The reflected beam becomes round on the PD when the beam is out of focus on the disc. Then the FOCUS SERVO system tries to keep the Objective-lens out of focus and the beam spot on the signal surface is kept large causing crosstalk.

#### Fig. 15 Distance between Two Lenses

The Objective-lens, which is closer (farther) to Cylindrical-lens than the optimum, makes the spot on the PD oval when focused and causes it to generate a positive (negative) voltage. The beam can be kept focused on the signal surface leaving the spot on the PD oval by applying OP amplifier with a bias current for compensating or cancelling the error signal. However, this narrows the focus servo range and makes the beam hard to be refocused if it defocuses largely by scratches or dirt on the disc. Applying offset bias current is, therefore, not recommended. (CLD-900, LD-707, etc. have a Focus Balancer to solve the problem.) However, lens deviation on the Z-axis can be detected by applying this focus offset.

However, lens deviation on the Z-axis can be detected by applying this focus offset.

Fig. 15 c. Applying Bias Voltage

#### b. Checking the lens deviation on Z-axis

(1) Play a Test Disc.

(2) Adjust the FOCUS OFFSET POT to make the RF signal the maximum. Some units will become out of focus when you turn it excessively.

(3) Stop playing and measure the focus-error DC voltage in the STANDBY mode. The position of Pickup on Z-axis is optimum if the voltage is 0V. Replace Pickup if the voltage is out of the  $\pm 0.2V$  range.

(4) Finally, adjust the Focus-offset-adjustment-POT to make the focus error voltage 0V in STANDBY mode.

#### 4. Mechanism Check

Now we can diagnose the Pickup. Mechanism and electronic circuits, however, should also be taken into consideration in diagnosing players because the Pickup is not working alone. Let's discuss the way of checking the mechanism. Mechanical deviation can be found visually. Electronic checkup is required to make it more accurate although our eyes are considerably accurate.

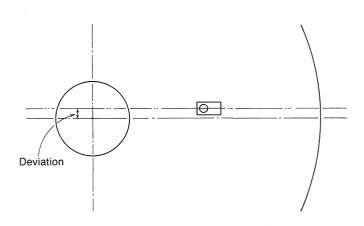

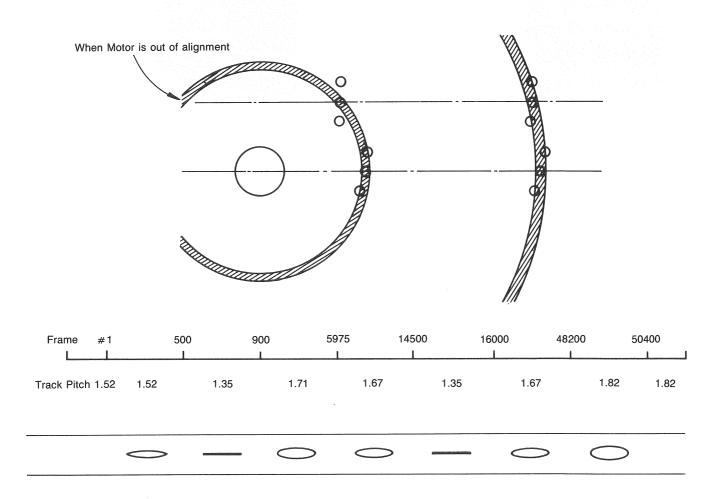

#### 4-1 Non-aligned Motor

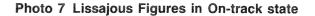

If the motor shaft is not aligned on the line on which Objective-lens travels, the symptom is the same as that of deviated Grating adjustment because the Tracking Servo is affected by it. In this case, after grating adjustment, the trouble is solved only at the Frame where it is adjusted, and the grating deviation increases as the Pickup moves far from the Frame. Grating adjustment is usually made in the midway on the disc. TRACK SKIPPING or NO PLAY will, therefore, result on inner or outer tracks.

Motor shaft alignment can be checked by comparing Lissajous figures of TRKG (A-B) and TRKG (A + B) keeping the tracking servo loop open as in Grating adjustment. The figures should stay unchanged on inner and outer tracks.

Fig. 16 Non-aligned Motor

#### A simple checking method

(a) Connect TRKG (A-B) and TRKG (A + B) to X and Y channels of an oscilloscope respectively.

(b) SEARCH throughout a disc from the inmost track to the outmost or vice versa.

(c) Observe the Lissajous figures while searching because Tracking Servo opens and the figures may vary this time. If it is not a horizontal line, grating should be adjusted. If it grows thick on inner or outer tracks, the motor should be realigned.

Note: A CAV disc available on the market is recommended for checking motor alignment because the track pitch of an F-series test disc differs by frame-ranges and the thickness of the Lissajous figures normally shifts as the Pickup travels as shown in Fig. 17. With the CAV disc available on the market, the alignment is all right as long as the figure does not change although it may be thick. If the motor is deviated, adjust Grating on tracks midway or farther and then adjust the motor position on inner tracks observing Lissajous figures.

In case you use an F-series test disc, to avoid misadjustment, adjust the Grating on outer tracks by making the Lissajous figures a vertical line (on-track state\*) and then adjust the motor position on inner tracks so that it becomes a vertical line, and finally readjust the Grating to make it a horizontal line to get an optimum Grating angle. Refer to "LD-motor position" of the service manual of CLD-909 for the details.

Fig. 17 Lissajous Figures Shifts As Pickup Travels

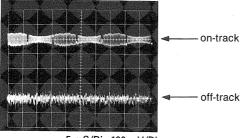

#### Note: ON TRACK

When adjusting the Grating, open Tracking Loop and find out the position where the envelope of TRKG error signal becomes clear and where the amplitude becomes the minimum by turning Grating adjustment screw. This time the three beams trace the center of the same track and the Lissajous figures become a vertical line. The state and position are called "ON TRACK" and "NUL POINT" respectively.

Fig. 18 ON-TRACK state

5 mS/Div 100 mV/Div

Xch: TRKG error signal Ych: TRKG (A + B) signal

A: T1 — F — T1' X: 20 mV/Div Y: 20 mV/Div

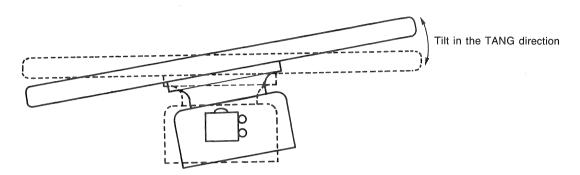

## 4-2 Tilted Spindle-motor from the tracking direction

What will happen if the motor is out of perpendicular to the locus of Pickup? The symptoms are the same as those when playing a warped disc. In case of LD-707 and CLD-909, this trouble occurs if the Pickup is not parallel to the Slider-base. The symptoms are:

- \* Crosstalk appears.

- \* Focus Lock becomes difficult.

- \* Pickup goes out of focus as it moves outward.

The players which have a Tilt Servo system can keep Pickup parallel to the disc to some extent. The distance between them, however, can not be kept constant.

Fig. 19 Tilted Motor from TRKG Direction

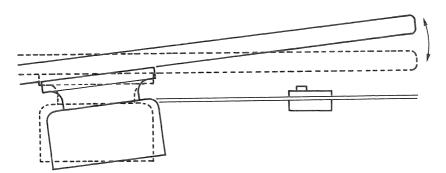

#### Checking the tilt of Pickup or Spindle-motor

- \* Observe Focus-return voltage filtered by LPF on an oscilloscope.

- \* Verify that the DC voltage does not vary on inner and outer tracks.

- \* In case of 12" disc, check it on midway and inner tracks of a less warped disc. If there is a difference of more than 0.1V in FOCUS-Return voltage between the readings on inner and center (midway) tracks, the Motor or Pickup can be considered to be tilted.

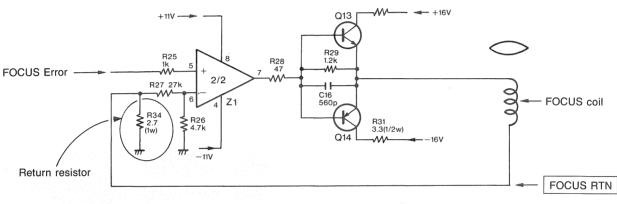

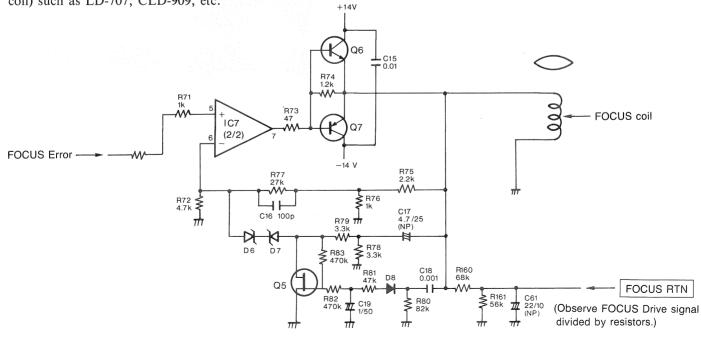

#### **Test Point**

Models which have a series circuit of Focus-coil and Return-resistor such as LD-1100, LD-700, P-D70, etc.

Fig. 21 Test Point of LD-1100, LD-700, P-D70, etc.

Models which have no Return-resistor (grounded Focuscoil) such as LD-707, CLD-909, etc.

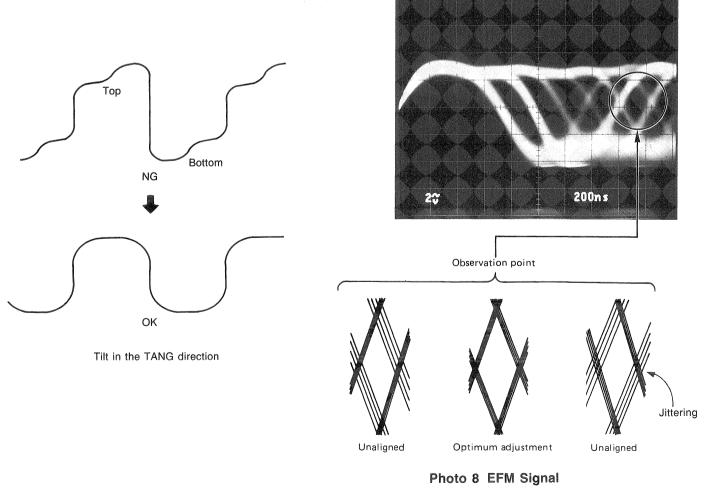

## 4-3 Tilted Spindle-motor from the tangential direction

What will happen when the Motor or Pickup tilts from the tangential direction?

*LD player:* Crosstalk — Adjust the perpendicularity of Motor or Pickup to obtain the maximum RF signal.

*CD player:* Dropout — Observe RF (EFM) signal waveform at the infinity-0 point on TRK #23 of Test Disc

(YEDS-7). Adjust them to make the top and bottom portions of the trace line horizontal on the oscilloscope.

On the models which generate obscure waveforms such as PD-5010 series, judge it observing the jitter component of EFM signal.

Fig. 23 Tilted Motor From TANG Direction

#### 5. Eccentricity

Every disc and motor has eccentricity to some extent. It is compensated by TRKG and TANG servo systems and CCD (Charge-Coupled Device). The beam skips tracks or SPDL Lock is released when the eccentricity is too large.

The degree of the symptom varies every time the disc is reloaded because it depends on the clamping conditions. Try to take the disc out, turn it by 90° and load it again. The causes of the eccentricity are:

- \* Worn Clamper or Clamper-bearing

- \* Faulty peripheral component of Clamper

- \* Barrs or wearing of the center hole of the disc

If the player sometimes skips, find out whether the player is eccentric or Pickup itself is faulty by the following method.

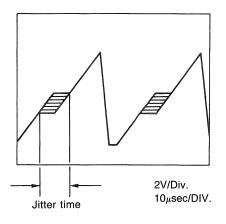

#### Measuring method of disc eccentricity

- 1. Play a disc, and open the TANG SERVO (or CCD SERVO) loop. To open the loop, refer to the following page and the adjustment process in Service Manual.

- 2. Observe the trapezoid waveform signal for generating TANG (CCD) Error, and measure the jittering period on an oscilloscope.

Jitter timeEccentricityLess than  $20\mu$ secNormal $20 - 30\mu$ secA little large $30\mu$ sec or more Causes skipping

Note: With a CAV disc measure the jitter time on inner tracks (between frames #1 and #5,000). The time becomes shorter as the Pickup moves outward. With a CLV disc, the jitter time is almost constant irrespective of tracking position.

3. If the measurement results are excessive with every scratchless disc, LV players may be faulty due to the faulty SPDL-motor shaft, clamper, or faulty clamper-shaft-holder.

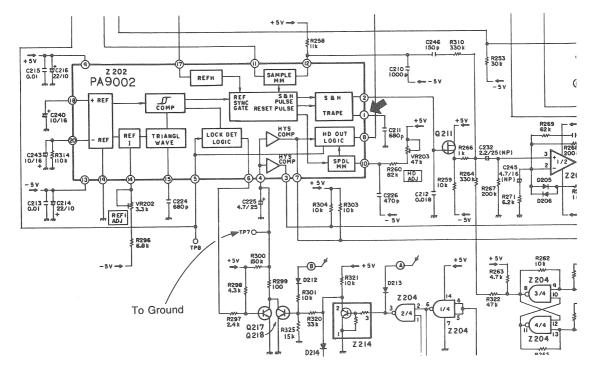

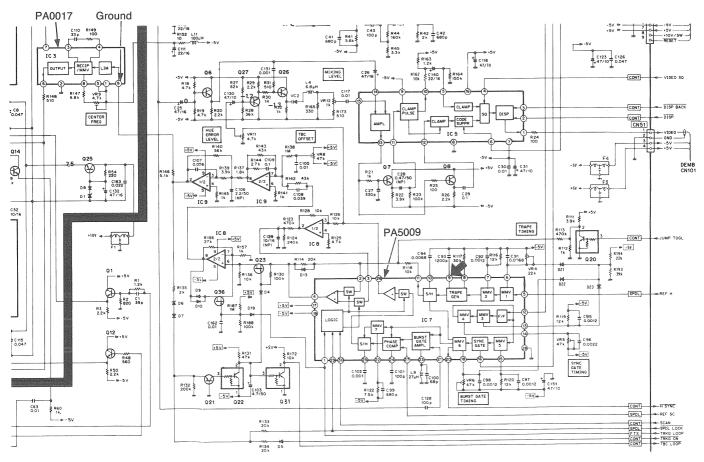

The arrows in the Fig. 25 and 26 show the test points for this measurement. As for other models, refer to the respective service manual and measure it in the same way as this. In case of LD-700, ground the TP7 to open the Tangential Servo and observe the signal at Z202 (PA9002)-1 on the oscilloscope. In case of LD-707, open CCP Servo by grounding IC3 (PA0017)-9 and observe it at IC7 (PA5009)-9.

Fig. 24 Jitter Time

Fig. 26 Measuring Jitter-time of LD707

28

#### 6. Overall checkup of Optical Pickup System

Let's summarize the check points.

a. Spindle-motor does not turn when a disc is loaded and PLAY is pressed.

Laser Diode does not glow so bright as He-Ne tube due to it's wave length. If a part of Objective-lens is bright in red, the Laser Diode is on.

Partially gleams in red

#### Photo 9 FOCUS (Objective) Lens

b. Spindle-motor starts rotating after a Disc is loaded and PLAY is pressed. (SPDL SERVO does not lock but skips, etc.)

Note: If it stops soon but keeps rotating when Tracking Servo is opened, check it on the four following items keeping the servo opened.

| Tracking Servo Loop | Observation Points                       | Items<br>Grating<br>Play a Test-disc.<br>Lissajous figures become a horizontal line at the prescribed<br>Frame                        |  |  |

|---------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Open                | X-ch: TRKG (A – B)<br>Y-ch: TRKG (A + B) |                                                                                                                                       |  |  |

| Open                | TRKG (A–B)                               | TRKG Balance<br>TRKG (A – B) signal center: 0V?                                                                                       |  |  |

| Open                | X-ch: TRKG (A – B)<br>Y-ch: TRKG (A + B) | SPDL motor alignment<br>Lissajous figures should not grow fat when searched in both<br>directions.                                    |  |  |

| Open or Close       | FOCUS RTN through LPF                    | Tilt in TRKG direction<br>DC voltage should be stable when Pickup is moved to inner or outer<br>tracks.                               |  |  |

| Close               | RF                                       | Tilt in TANG direction<br>CD: Top and bottom portions of RF (EFM) signal should be flat.<br>LD: Amplitude of RF signal should be max. |  |  |

#### Table Checking Beam Path

# **Microcomputer Fundamentals**

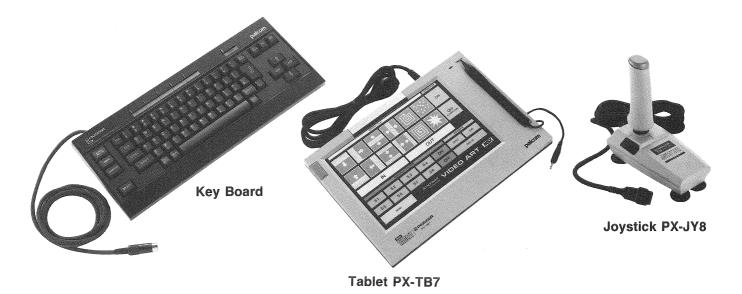

The microcomputer is a tiny computing system. The equipment itself is called "hardware". Program instructions or the way of using it is called "software". The software permanently stored in a ROM (read only memory) is called firmware. Its main blocks have been integrated into one or a few LSI's. The difference from the minicomputer and the larger computer is in size, speed of execution, computing power and price. The miniaturizing technique of electronic circuits has given the microcomputer an ability close to that of old large computers.

The microprocessor, or central processing unit (CPU) which is the brain of the microcomputer, is being employed in various equipment and controls their functions. The knowledge of computers is usually unnecessary for our repair service because most operations are performed inside the LSIs and the CPU can be considered to be a black box. Troubleshooting those equipment, however, will be easy if you have the knowledge. Here we will discuss the fundamental principle of the microcomputer basing on the Zilog Z80ACPU. Refer to its instruction manual for details. Photo 1 shows our PX-7, MSX Personal Computer in European version which employs a Z80A.

PX-7, MSX Personal Computer in European Version

Photo 1

#### 1. Number Systems

Digital computers use the binary system although we are accustomed to the decimal system. A digital signal has only two states, low (L) and high (H) or 0 and 1. They also use octal and hexadecimal systems because the unit of the processor in computers is 4 and 8 bits. Table 1 shows their differences. As for the details, refer to the "DIGI-TAL — Supplement of TUNING FORK".

| Decimal | Binary | Octal | Hex | BCD       |

|---------|--------|-------|-----|-----------|

| 0       | 0      | 0     | 0   | 0000 0000 |

| 1       | 1      | 1     | 1   | 0000 0001 |

| 2       | 10     | 2     | 2   | 0000 0010 |

| 3       | 11     | 3     | 3   | 0000 0011 |

| 4       | 100    | 4     | 4   | 0000 0100 |

| 5       | 101    | 5     | 5   | 0000 0101 |

| 6       | 110    | 6     | 6   | 0000 0110 |

| 7       | 111    | 7     | 7   | 0000 0111 |

| 8       | 1000   | 10    | 8   | 0000 1000 |

| 9       | 1001   | 11    | 9   | 0000 1001 |

| 10      | 1010   | 12    | А   | 0001 0000 |

| 11      | 1011   | 13    | В   | 0001 0001 |

| 12      | 1100   | 14    | С   | 0001 0010 |

| 13      | 1101   | 15    | D   | 0001 0011 |

| 14      | 1110   | 16    | E   | 0001 0100 |

| 15      | 1111   | 17    | F   | 0001 0101 |

| 16      | 10000  | 20    | 10  | 0001 0110 |

| 17      | 10001  | 21    | 11  | 0001 0111 |

| 18      | 10010  | 22    | 12  | 0001 1000 |

| 19      | 10011  | 23    | 13  | 0001 1001 |

| 20      | 10100  | 24    | 14  | 0010 0000 |

There are several ways to represent data using the binary code such as straight binary, signed binary, 2's complement, binary coded decimal (BCD) and American Standard Code for Information Interchange (ASCII).

#### 1.1 Straight Binary

In unsigned representation, an n-bit binary data word is simply used to represent the first  $2^n$  nonnegative integers. An 8-bit data word can represent the integers 0 through 255 as shown on Table 2.

| Table | 2 | Straight | Binary | Representation |

|-------|---|----------|--------|----------------|

|-------|---|----------|--------|----------------|

| Straight              |                 |

|-----------------------|-----------------|

| binary representation | Decimal numbers |

| 00000000              | 0               |

| 0000001               | 1               |

| 0000010               | 2               |

| 0000011               | 3               |

| 00000100              | 4               |

|                       |                 |

| ÷                     |                 |

| ·                     |                 |

| 11111111              | 255             |

#### **1.2 Signed Binary**

Representation of both positive and negative numbers with the straight binary is impossible. The signed binary spares the most significant bit (MSB) for representing the sign of the numbers. The lower-order bits are used to represent the absolute value in straight binary as shown in Table 3. This is seldom used for two reasons. First, there are two representations for the number zero. Second, the ordinary rules of addition for straight binary cannot be applied to signed binary numbers.

| Table 3 | Signed | Binary | Representation |

|---------|--------|--------|----------------|

|         |        |        |                |

| Signed binary representation | Decimal numbers |

|------------------------------|-----------------|

| 011111111                    | + 127           |

| 011111110                    | + 126           |

| •                            | •               |

|                              | . 2             |

| 000000001                    | 1               |

| 000000000                    | 0               |

| 10000000                     | 0               |

| 10000001                     | - 1             |

| 10000010                     | -2              |

| •                            |                 |

|                              | 126             |

| 111111111                    | - 126           |

#### 1.3 BCD

Each decimal digit can be represented by a combination of four binary numerals. 4 bits can represent 16 codes. 10 codes from 0000 to 1001 among the 16 codes are used for binary representation. Other combinations are not used in this system. This is useful for interfacing numeric keyboards and displays. Refer to Fig. 1.

| Examples |      |             |

|----------|------|-------------|

| 3        | 9    | Decimal (D) |

| 0011     | 1001 | Binary (B)  |

| 6        | 5    | Decimal     |

| 0110     | 0101 | Binary      |

#### Fig. 1 BCD Representation

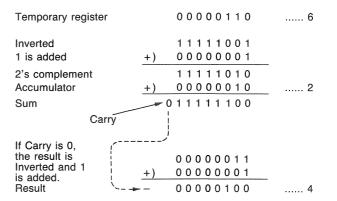

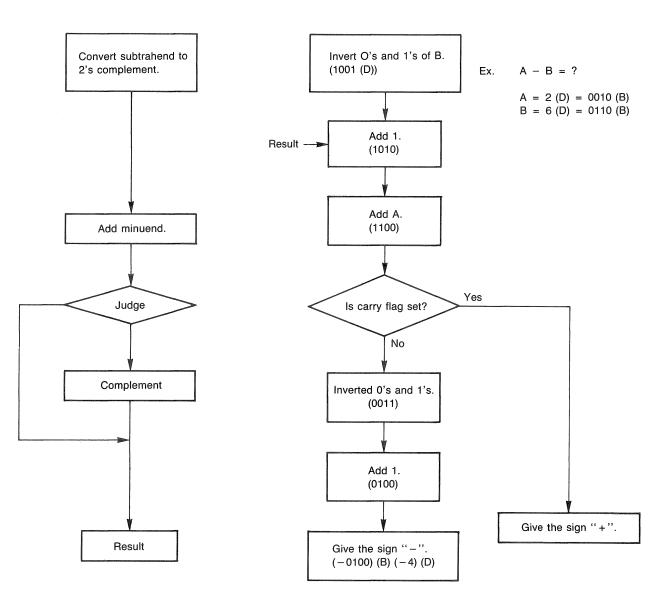

#### 1.4 2's complement

2's complement notation is most commonly used in microcomputers for performing arithmetic with signed numbers. In this notation, the negative of a binary number is represented as its 2's complement. A complement of a number is formed simply by changing the 1's to 0's and the 0's to 1's. The 2's complement of a number is formed by adding one to the complement of the number.

| Example         |          |                   |

|-----------------|----------|-------------------|

| Straight binary | 00001010 | 10 in decimal (D) |

| Changing        | 11110101 | Complement        |

| + 1             | 11110110 | 2's Complement    |

As mentioned 256 different numbers can be represented by 8 bits. The 0 on the MSB represents a positive number and 1 represents a negative one. If 011111111 represents +127 and is counted down, 0, -1 and -128 become 00000000, 11111111 and 10000000 respectively.

The numbers from +127 to -128 are available by decrimenting or incrementing throughout the range.

| Table | 4 | 2's | Complement |

|-------|---|-----|------------|

|-------|---|-----|------------|

| Twos complement | Decimal number |

|-----------------|----------------|

| 01111111        | 127            |

| 01111110        | 126            |

|                 | •              |

| 0000010         | 2              |

| 0000001         | 1              |

| 00000000        | 0              |

| 11111111        | - 1            |

| 11111110        | -2             |

| 11111101        | -3             |

| •               | :              |

|                 |                |

| 1000001         | - 127          |

| 10000000        | - 128          |

|                 |                |

#### 1.5 ASCII

In ASCII notation 7 bits of one byte code are used for representing decimal numbers, alphabetical characters and machine control commands. The MSB of the code is used for parity or error testing. The seven bits provides 128 possible characters. Decimal numbers are represented as Table 5a. 32 combinations are assigned to control commands which are not printed out but provided to handle hardware operations.

| Р      | ASCII code | Decimal number |

|--------|------------|----------------|

|        | 0110000    | 0              |

|        | 0110001    | 1              |

|        | 0110010    | 2              |

|        | 0110011    | 3              |

| Parity | 0110100    | 4              |

|        | 0110101    | 5              |

|        | 0110110    | 6              |

|        | 0110111    | 7              |

|        | 0111000    | 8              |

|        | 0111001    | 9              |

|        | 3 0 ~ 9    |                |

#### Table 5a Decimal Number to ASCII Codes

### Table 5b ASCII Codes Represented byHexadecimal Numbers

|     |        |     |        |     |        |        |        | 1                                     |

|-----|--------|-----|--------|-----|--------|--------|--------|---------------------------------------|

| Hex | Symbol | Hex | Symbol | Hex | Symbol | Hex    | Symbol |                                       |

| 00  | NUL    | 20  | SPACE  | 40  | @      | 60     |        |                                       |

| 01  | SOH    | 21  | 1      | 41  | Ä      | 61     | a      |                                       |

| 02  | STX    | 22  | ,,     | 42  | В      | 62     | b      |                                       |

| 03  | ETX    | 23  | #      | 43  | c      | 63     | c c    |                                       |

| 04  | EOT    | 24  | \$     | 44  | D      | 64     | d      |                                       |

| 05  | ENQ    | 25  | %      | 45  | E      | 65     | e      |                                       |

| 06  | ACK    | 26  | &      | 46  | F      | 66     | f      | Parity                                |

| 07  | BEL    | 27  | ,      | 47  | G      | 67     | g      |                                       |

| 08  | BS     | 28  | (      | 48  | н      | 68     | ĥ      |                                       |

| 09  | нт     | 29  | ì      | 49  | 1      | 69     | i      | 6 B(H)                                |

| 0A  | LF     | 2A  | *      | 4A  | J      | 6A     | j      | ¥                                     |

| OB  | VT     | 2B  | +      | 4B  | к      | (6B    | k)     | ───────────────────────────────────── |

| 0C  | FF     | 2C  | ,      | 4C  | L      | 6C     | l i    |                                       |

| ID  | CR     | 2D  |        | 4D  | м      | 6D     | m      |                                       |

| 0E  | so     | 2E  |        | 4E  | N      | 6E     | n      |                                       |

| 0F  | SI     | 2F  | 1      | 4F  | 0      | 6F     | 0      |                                       |

| 10  | DLE    | 30  | 0      | 50  | Р      | 70     | р      |                                       |

| 11  | DC1    | 31  | 1      | 51  | Q      | 71     | q      |                                       |

| 12  | DC2    | 32  | 2      | 52  | R      | 72     | r      |                                       |

| 13  | DC3    | 33  | 3      | 53  | S      | 72     | s      |                                       |

| 14  | DC4    | 34  | 4      | 54  | Т      | 74     | t      |                                       |

| 15  | NAK    | 35  | 5      | 55  | U      | 75     | u      |                                       |

| 16  | SYN    | 36  | 6      | 56  | V      | 76     | v      |                                       |

| 17  | ETB    | 37  | 7      | 57  | W      | 77     | w      | LF = Line Feed                        |

| 18  | CAN    | 38  | 8      | 58  | Х      | 78     | ×      | FF = Form Feed                        |

| 19  | EM     | 39  | 9      | 59  | Y      | 79     | У      | CR = Carriage Return                  |

| 1A  | SUB    | ЗA  | :      | 5A  | Z      | 7A     | z      |                                       |

| 1B  | ESC    | 3B  | ;      | 5B  | [      | 7B     |        | CTRL = Control Character              |

| 1C  | FS     | 3C  | <      | 5C  | \      | 7C     |        | BS = Backspace                        |

| 1D  | GS     | 3D  | =      | 5D  | ]      | 7D     |        | HT = Horizontal tab                   |

| 1E  | RS     | ЗE  | >      | 5E  | ٨      | 7E     | ~      | VT = Vertical tab                     |

| 1F  | US     | 3F  | ?      | 5F  | -      | 7F     | DELETE | DEL = Rub out                         |

| L   | I      | u   |        | U   | L      | Lauran | 1      |                                       |

Codes in squares are for operating hardware

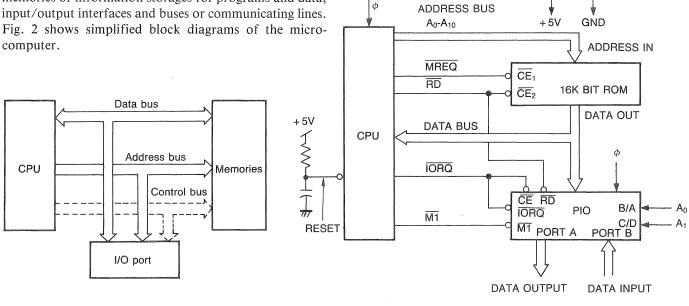

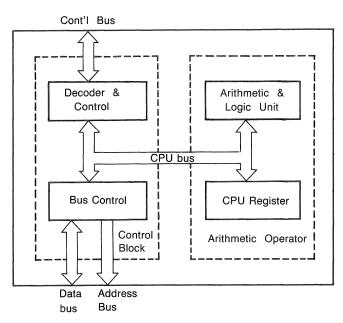

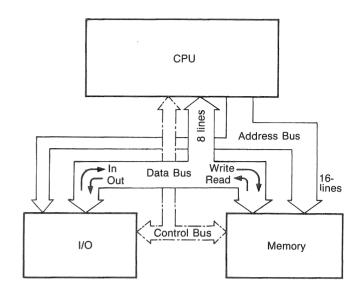

#### 2. Architecture

The hardware of the microcomputer consists of a CPU, memories or information storages for programs and data, input/output interfaces and buses or communicating lines. computer.

OSC

(a) The Simplest Diagram

(b) Small Computer System Using a Z80ACPU

+5 VOLT

POWER SUPPLY

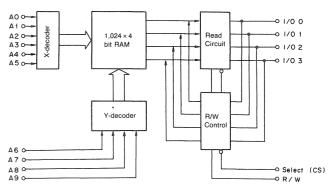

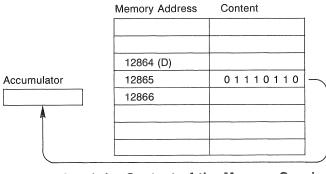

#### 2.1 Memories

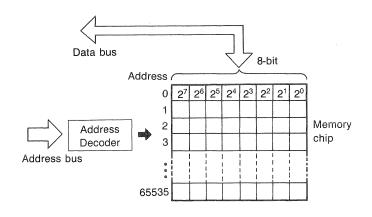

Microprocessor systems use binary memories to store programs and data. Now a 1/3-square-inch chip of a memory device has a capacity of over 65k bits. It can store more than 8 thousand alphanumeric characters. Each of the memories has its own address. The address decoder on the memory chip decodes the address data and connects the selected memory to the data pins. Fig. 3 shows a simplified diagram of an 8-bit memory.

Fig. 3 8-bit Memory Device

ROM: The information is stored permanently or semipermanently and is read out, but not altered in operation.

RAM (Ramdom-access Memory): A Read/Write memory into which data can be stored and then retrieved.

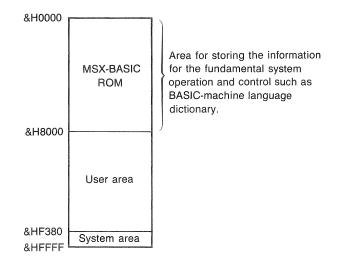

Fig. 4 Simplified Memory Map of PX-7

#### The principle of ROM

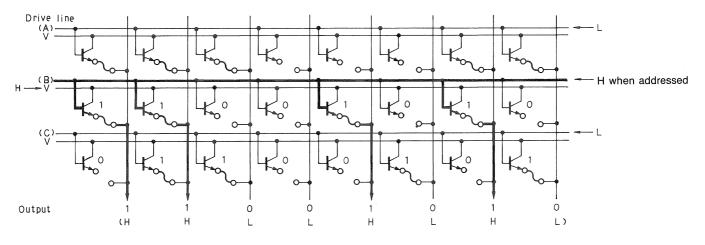

One of the simple memory devices is a transister. A transistor can memorize one bit of information by keeping its base open or closed. Fig. 5 shows the magnified diagram of the FUSE ROM. The eight transistors hanging on the same drive line consist a set of memories that has one address. A set of binary information (11001010) is available at the output when the power V is supplied to the circuit and the addressed drive line (B) is made H, because the source current flows only through the transistors connected at the emitters, and the level on the output lines disconnected from the transistors stays L. Other set of transistors are kept inactive because their drive lines are kept L.

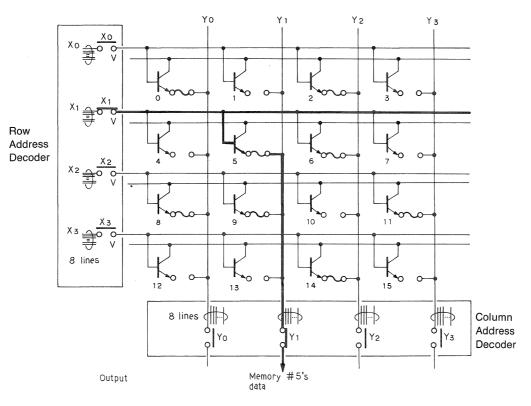

Fig. 6 shows a ROM that has sixteen 1-bit memories. The data of memory #5 appear at the output when  $X_1$  and  $Y_1$  are closed. Usually there are eight bits in one memory unit and eight lines for the output.

Fig. 6 Addressing Memory Matrix

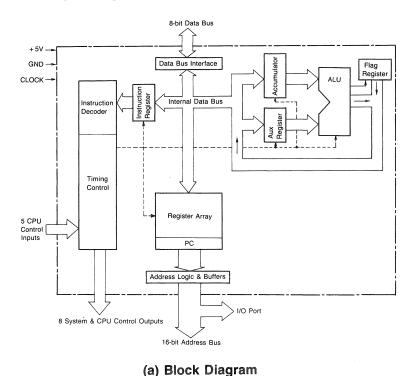

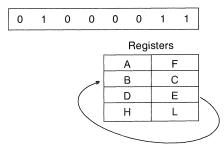

## 2.2 CPU

Fig. 7 shows the simplified block diagram of the CPU. It receives data from memory and external devices, processes them and puts out the result controlling the operation of the whole system.

The CPU can perform a great variety of tasks depending on the software. However, it just reads instructions that come from memories or external devices and executes them. Those appliances of particular purposes such as washing machines are not computers even they employ microprocessors because they are operated only by a few nonflexible programs.

Fig. 7 Simplified Block Diagram of CPU

Devices in CPU

ALU (Arithmetic and Logical Unit)

This is an adder made of logic circuits such as AND, OR and Exclusive-OR and performs arithmetic and logical operations supplemented by shifting and sequencing circuitry for implementing multiplication, division, etc.

| MAIN REG S       | ET                                      | ALTERNA          |    |             |                    |  |  |  |  |

|------------------|-----------------------------------------|------------------|----|-------------|--------------------|--|--|--|--|

| ACCUMULATER<br>A | FLAGS<br>F                              | ACCUMULATO<br>A' | DR | FLAGS<br>F' |                    |  |  |  |  |

| В                | с                                       | B'               |    | C'          | OFNERAL            |  |  |  |  |

| D                | E                                       | D'               |    | E'          | GENERAL<br>PURPOSE |  |  |  |  |

| н                | L                                       | H'               |    | Ľ'          | REGISTERS          |  |  |  |  |

|                  | INTERRUPT<br>VECTOR<br>I<br>INDEX REGIS |                  |    | SPECIAL     |                    |  |  |  |  |

|                  | INDEX REGIS                             | STER IY          |    | REGISTER    | s                  |  |  |  |  |

(b) Register Array

STACK POINTER SP

PROGRAM COUNTER PC

u u

Fig. 8 Z80A CPU

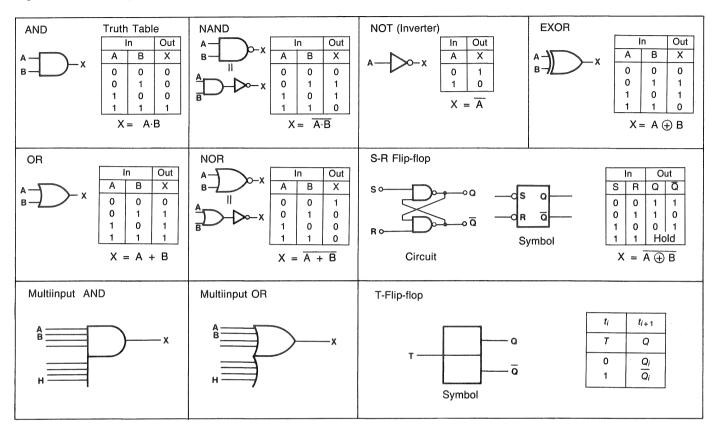

Logic devices

Fig. 9 shows the basic AND, NAND, OR, NOR, NOT EOR, and flip-flop circuits. Flip-flops are widely used as register and memory devices.

Fig. 9 Logic Devices

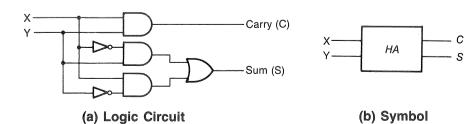

## Half adder

This accepts two binary input signals and produces corresponding sum and carry outputs and has no carry input from the previous stage.

(c) Truth Table

Fig. 11 Half Adder

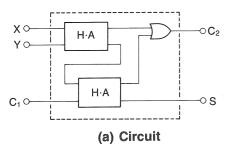

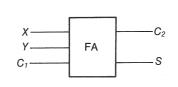

#### Full adder

This accepts two binary digits to be added and a carry digit from the previous stage and produces sum and carry outputs.

(b) Symbol

|   | Add |                | Result |                |  |  |  |

|---|-----|----------------|--------|----------------|--|--|--|

| Х | Y   | C <sub>1</sub> | S      | C <sub>2</sub> |  |  |  |

| 0 | 0   | 0              | 0      | 0              |  |  |  |

| 0 | 0   | 1              | 1      | 0              |  |  |  |

| 0 | 1   | 0 1            |        | 0              |  |  |  |

| 0 | 1   | 1              | 0      | 1              |  |  |  |

| 1 | 0   | 0              | 1      | 0              |  |  |  |

| 1 | 0   | 1              | 0      | 1              |  |  |  |

| 1 | 1   | 0              | 0      | 1              |  |  |  |

| 1 | 1   | 1              | 1      | 1              |  |  |  |

|   |     |                |        |                |  |  |  |

$$\begin{split} S &= X \cdot Y \cdot C_1 + \overline{X} \cdot Y \cdot \overline{C}_1 + \overline{X} \cdot \overline{Y} \cdot C_1 + X \cdot \overline{Y} \cdot \overline{C}_1 \\ C_2 &= X \cdot Y + X \cdot C_1 + Y \cdot C_1 \end{split}$$

(c) Truth Table

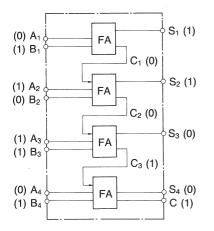

Fig. 13 shows a 4-bit parallel adder. If 0110 and 1101 are added, inputs and outputs are as follows:

| Bits      | Carry | 4 | 3 | 2 | 1 |  |  |  |  |  |

|-----------|-------|---|---|---|---|--|--|--|--|--|

| Inputs A  |       | 0 | 1 | 1 | 0 |  |  |  |  |  |

| Inputs B  |       | 1 | 1 | 0 | 1 |  |  |  |  |  |

| Inputs C  | 0     |   |   |   |   |  |  |  |  |  |

| Outputs S | 1     | 0 | 0 | 1 | 1 |  |  |  |  |  |

|           |       |   |   |   |   |  |  |  |  |  |

Carry

Fig. 13 4-bit Parallel Adder

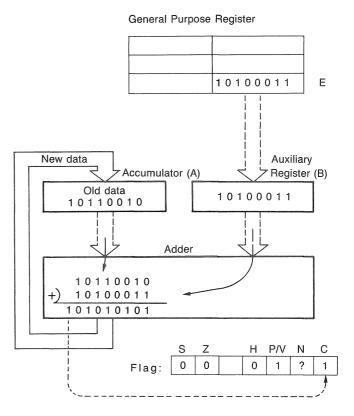

Accumulator (A-register)

A register for temporarily storing a number before and after arithmetic, logical or transferral operation.

#### Temporary Register (B-register)

This is the subsidiary register for Accumulator, holds one of the arithmetic operands and delivers it to the ALU.

Instruction Register (Control register)

This retains the code of the instruction currently being executed.

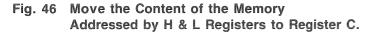

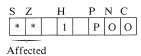

Flag Register

| 7 | 6 | 5 | 4 | 3 | 2   | 1 | 0 |

|---|---|---|---|---|-----|---|---|

| S | Z |   | Н |   | P/V | N | С |

The result of operation or the current conditions of the computer are stored here. Referring to the conditions the computer determines what to do next. For example, you can jump and stop the operation by arranging the program:

If EVEN, JUMP to address 8500 If NEGAtive, JUMP to address 8600 If ZERO, STOP

- S: Sign flag. This bit becomes "1" if the result of arithmetic operation is negative.

- Z: Zero flag. "1" if the result of the operation is zero.

- H:Half-carry flag. "1" if the add or subtract operation produced a carry into or borrow from bit-4 of the accumulator.

Refer to DAA, page 56.

- P/V: Parity or overflow flag. Parity and overflow share the same flag. Logical operations affect this flag with the parity of the result while arithmetic operations affect this flag with overflow of the result. If P/V holds parity and if the result of the operation is even, "1". If P/V holds overflow and the result of the operation produced an overflow, "1".

- N: Add/Subtract flag. "1" if the previous operation was a subtract.

H and N are used in conjunction with the decimal adjust instruction (DAA) to correct the result in BCD arithmetic. The knowledge of these functions of this register is required for making a program although the contents of this register is not directly accesible to programmers.

C: Carry flag. "1" if the operation produced a carry from the MSB of the operand or result.

Bits 3&5: Not used

#### General-purpose Registers

Internal addressable registers in a CPU that can be used for temporary storage, as accumulators, index registers, stack pointers, or for any other general-purpose functions.

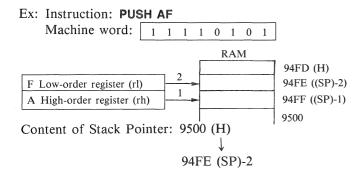

#### Special Registers

*Stack pointer:* When a program is sustained, the interim result should be stored somewhere in the memory to be used later. This enables the CPU to process "stack" of data using the last-in first-out (LIFO) method. This contains the address number of the current top or entry point of the stack of information. When an interrupting service is finished, the stacked information is popped or taken out for resuming sustained program. This will be discussed later.

*Program Counter:* This holds the address value of the memory location where the next CPU directive is to be obtained.

*Index Register:* This contains a quantity to be added to the address number of the instruction under the direction of the program for automatic and temporary address modification.

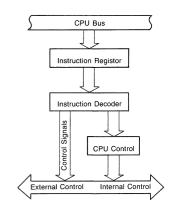

#### Control unit

This controls the operation of the whole computer system by directing the sequence of operation, decodes instructions and gives commands particular devices to start or stop.

#### Clock

The operation of the most microcomputers is synchronized with a clock signal. The operating speed of a computer depends on the clock frequency. Z80A employs a 4.0MHz external clock.

#### Buffers

In addition to impedance matching devices, these work as storages used to compensate for a difference in rate of flow of data, or time of occurrence of events when transmitting data from one device to another.

#### Shift register

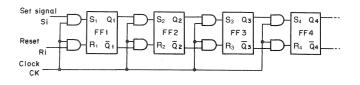

The following is a right-shift register. The inputs  $S_i$  and  $R_i$  have a correlation of  $S_i \neq R_i$  and appear in series synchronously to the clock signal. Q and  $\overline{Q}$  appear 1-clock later than the time when the inputs appear. They are shifted to the right one by a clock pulse. This is also used as a serial-parallel converter and a shifter for arithmetic and logic operation.

(a) Circuit

(b) Timing chart

Fig. 14 Shift Register

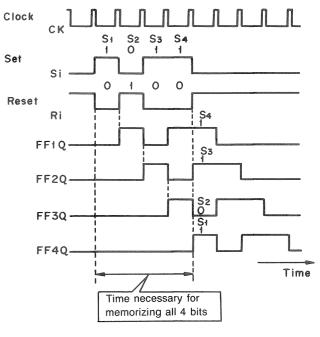

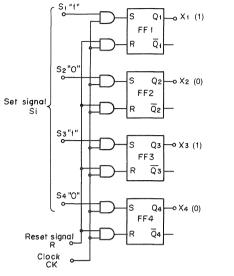

## Parallel register

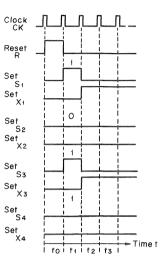

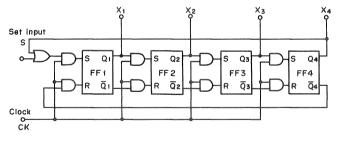

For storing information, this register is first cleared by Reset signal during to, then Set signal is applied to the

Clock ск

Set

FFIQ(X1)

FF2Q(X2)

FF3Q(X3)

FF4Q(X4)

s

S-inputs and only the flip-flops applied with "i" shift their

outputs during  $t_1$ . The outputs are kept unchanged till the

next Reset signal is applied.

(b) Timing Chart

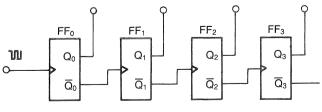

## Ring counter

This is a kind of shift registers, carries only one positive pulse at a time and is used for controlling the timing for reading and executing instructions.

(a) Circuit

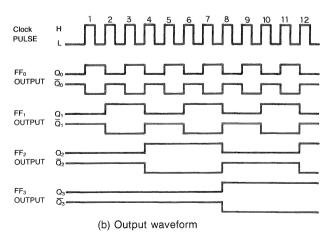

#### Binary counter

This produces one output pulse for every two input pulses and is used for the program counter.

(b) Timing Chart

► Time t

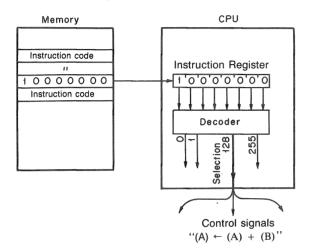

Decoder

This selects one or more output channels according to the combination of input signals, determines the meaning of an instruction from the combination and initiates a computer operation. If the instruction code is made of 8 bits, 256 kinds ( $2^8$ ) of outputs are available. Fig. 17 shows the way an operation code is fetched and decoded.

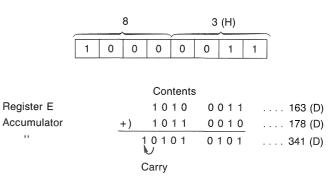

In the Z80A the instruction code "10000000" means that "Add the contents of A and B registers and place the result in the A register, or "(A)  $\leftarrow$  (A) + (B)".

Fig. 17 Instruction Decoding >

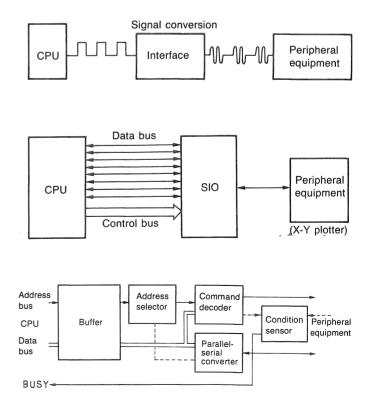

## 2.4 Interface

#### I/O Interface

The CPU understands only its own machine language made of binary codes while peripheral equipment deal with various types of signals. The interface is a common boundary between the CPU and peripheral equipment and adapts the signal requirements of the equipment to those of a computer and vice versa. Its functions are:

- a. Adjusting signal format, mode, characteristics and speed (Digital ↔ Analog, level, current, speed, etc.)

- b. Selecting one peripheral equipment from those connected

- c. Decoding a CPU's operation command and passing it to the equipment concerned

- d. Memorizing data temporarily

- e. Informing CPU of the conditions of the equipment or vice versa

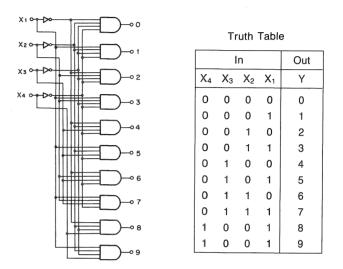

Many kinds of interfaces such as serial input-output interface (SIO) and parallel input-output interface (PIO) are required to deal with various peripheral equipments. PX-7 equips interfaces for LaserVision players and CRT display in addition to the MSX standard interface for keyboard, cassette recorder, TV monitor, joystick, tablet, etc. SIO arranges parallel data to serial or vice versa. Buffers adjust signal level, current and the timing of data transmission holding received data temporarily. If 10000000 (B) is applied from the Instruction Register to Decoder, 128th output is selected. The signal for performing the addition is applied to the devices concerned in CPU, and the instruction is executed. Fig. 18 shows a binary-decimal decoder.

Fig. 18 Binary Decimal Decoder

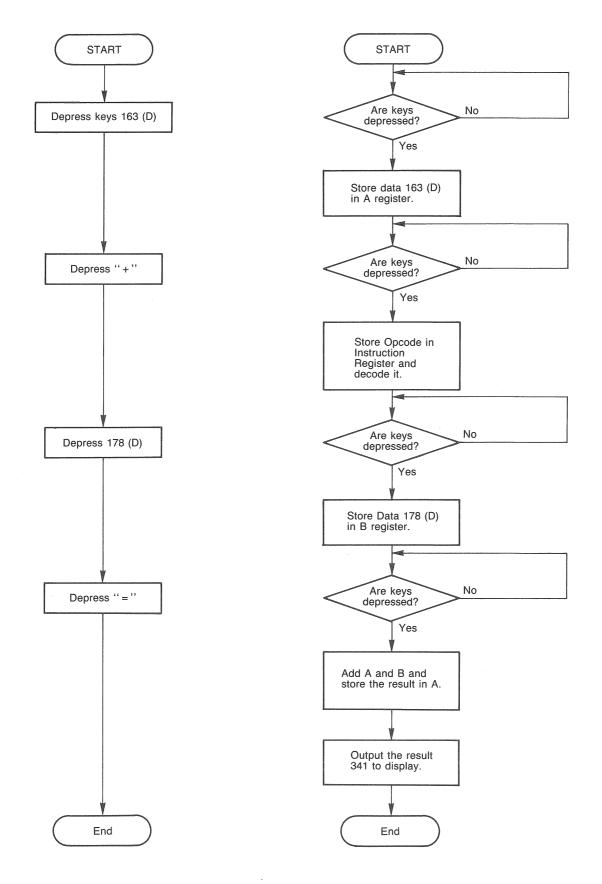

#### Keyboard

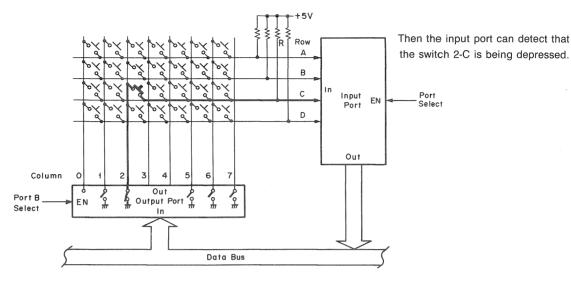

Let's see the basic operation of a keyboard. Fig. 19 shows the interface of the 32-key board. A program is required to scan the keyboard quickly. The output port scans the columns to set one of them low and the input port reads the rows in turn. If the key 2-C is pressed and the line 2-C is closed, the current flows from +5V to Column 2 through the R and the key switch 2-C, and the level at C is pulled down when the Column 2 is set low.

Fig. 20 Keyboard

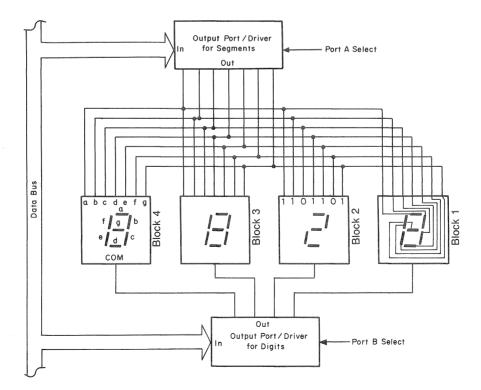

Character Display

In Fig. 21 the character blocks are quickly switched on and off in turn and only one of them is on at any moment. The outputs of the segment driver are changed synchronizing with the scan timing of the block driver. So the character information for the block 1 appears only when the block 1 is turned on.

Fig. 21 Character Display

#### 2.5 Bus Structure

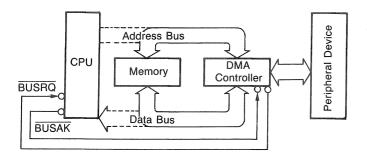

The bus is a set of wires over which information is transferred. Basic computer signals are address, data and control signals. A computer has an address bus, I/O port bus, data bus and control bus to let its devices exchange data with the processor. In the Z80A system I/Os and memories share the same bus.

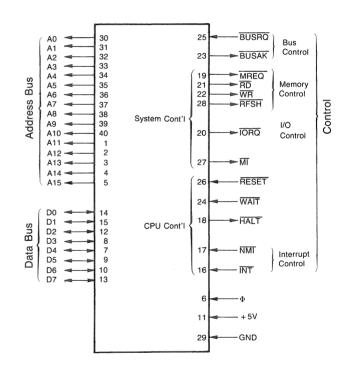

Address bus: A unidirectional bus over which appears digital information that identifies either a particular memory location or I/O device. No matter how many memory locations there may be, only one may be accessed at a time. The number of address lines of Z80A CPU is 16. 16-line address bus can address 65536 locations ( $2^{16}$ ) directly that can keep 65536-byte information because one memory location keeps 8-bit (or 1-byte) information.

*Data bus:* Bidirectional data lines. Z-80A has 8 data lines for sending 8-bit information in parallel at a time. Larger computers have separate input and output data buses. To save the bus lines, microcomputers use the 8 lines for both input and output purposes by sharing time. To commonly use the bus, a traffic controller is required.

*Control bus:* A set of control lines, usually from 10 to 100, with a function to carry the synchronization and control information necessary to the computer system. Z80A has 13 control lines, six lines for system control, five for CPU control and two for CPU bus control. The bus carries a signal to indicate whether the current transaction is a read or write from a memory or a peripheral, interrupt request or bus request signal, an extended cycle signal, and a response to indicate that the request of a peripheral device has been accepted and so on. Such signals might be interrupt, hold, acknowledge, read, write, etc.

Fig. 22 Bus Structure

Fig. 23 Terminals and Bus Lines of Z80A

#### **3-state Bus**

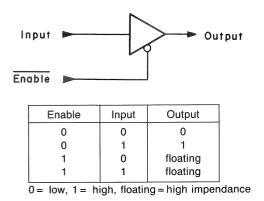

The microprocessor selects one device to talk to and disconnects the others with the help of the tristate drivers (or buffers) that enable the processor to selectively turn devices on and off. In Fig. 24, only when the Enable is low (L), the buffer passes the input signal to the output.

Fig. 24 Tristate Driver

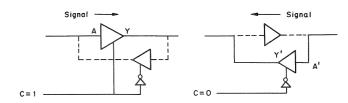

A bidirectional buffer can be formed with two tristate buffers and an inverter. The control signal determines the direction of signal flow.

Fig. 25 Bidirectional Buffer /

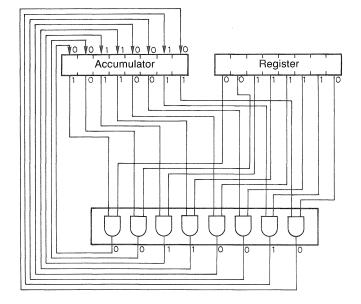

Fig. 27 shows how a memory cell is selected sharing one signal data line. When address number is 110 (B), the cell No. 6 (D) is selected and its data is put out on the data line.

D11 DO 1 D12 C D02 D13cActually 8 Flip-flops similar to this. Binary Select Data in D 14 Data out D04 D15 o DO 5 D160 D17 CP O consists of B Reset 0

Fig. 27 Selecting A Memory Cell

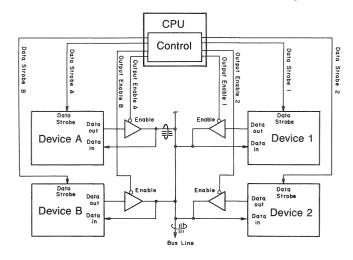

In Fig. 26 four devices share only one data line in communication.

Actually there are more senders and receivers. Each sender/receiver is provided with two control signals: Output Enable for its tristate driver and Data Strobe for input. The control logic permits only one sender to be active at a time. Other disabled drivers are in a high-impedance (floating) state and put out neither H nor L signal, and they have no effect on the logic state of the bus. When Device-A sends a piece of data to Device-2, the Control sets Output-enable-A true and all the other Output-enables false, and then sends a pulse on the line of Data-strobe-2 to let the Device-2 receive the data. RAMs are typical senders/receivers. This method saves connecting lines.

Fig. 26 Tristate Bus In Communicating System

In Fig. 28 the eight flipflops are enabled at a time, and put out parallel 8-bit data.

DO O

Enable /

Disable D10

Fig. 28 8-bit Register with Tristate Gates

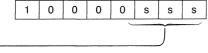

#### 2.6 Addressing structures

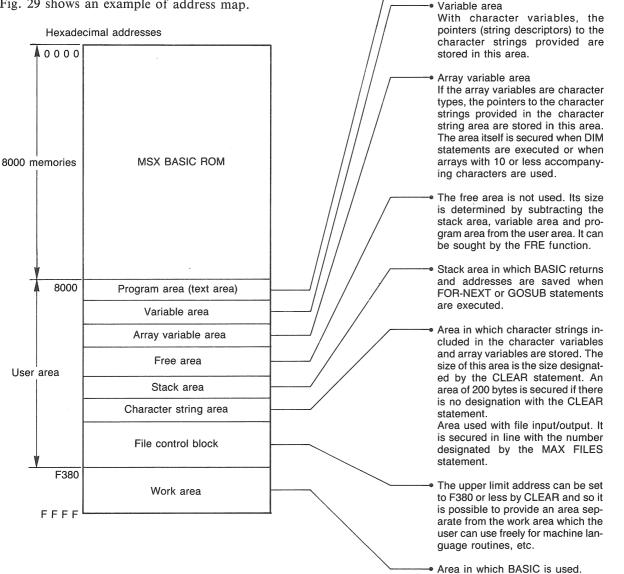

Each of the memories and other devices has an address. The address areas depend on the computer system. Fig. 29 shows an example of address map.

Fig. 29 Memory Map of PX-7

Selecting Memory Location

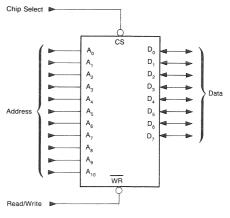

Fig. 30 shows a  $2K \times 8$  RAM. 2k RAM has 2,048 (2<sup>11</sup>) address locations and 16,384 bits (2,048 bytes  $\times 8$  bits). Each byte has its own address. The RAM has 10 address inputs, 8 data in/out terminals and one each of chip select and Read/Write (R/W) terminals. ROMs have no R/W terminal and the data bus is unidirectional because they can not be written. When writing, the Chip Select signal becomes true, address signal appears on the address bus, a particular memory location is waken up, data are placed on the data bus, and then the R/W signal is made low.

Area in which programs with line

numbers are stored.

Fig. 30 2K x 8 RAM

## Address Decoding

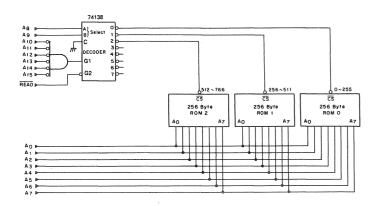

A microcomputer uses many memory chips and some serial addresses are assigned to each chip. If the chip has 256 locations, the number of the higher order byte of addresses will be the same. The higher order half of the address bus can be saved by decoding the 9th (A8) and 10th (A9) bits preliminary and selecting a memory chip. Fig. 31 shows that 256 addresses are assigned to each of three 256 byte ROMs. In Fig. 32, the address lines from A10 to A15 can be ANDed because the signal on the lines is always 0. A8 and A9 determine the chip to be selected. The information on the lower half of the address bus is applied to all chips, but only one selected chip reads the address at a time because the others are all disabled. 8 lines from A0 to A7 determine the memory location to be selected inside the memory chip.

|                  |         |    | F  | RON | N N | UMI | 3ER   |        |   | LO | CA           | LION | I WI | THI | N R  | OM |   |

|------------------|---------|----|----|-----|-----|-----|-------|--------|---|----|--------------|------|------|-----|------|----|---|

|                  | Address | 15 | 14 | 13  | 12  | 11  | 10    | 9      | 8 | 7  | 6            | 5    | 4    | 3   | 2    | 1  | 0 |

|                  | 0       | 0  | 0  | 0   | 0   | 0   | 0     | 0      | 0 | 0  | 0            | 0    | 0    | 0   | 0    | 0  | 0 |

|                  | 1       | 0  | 0  | 0   | 0   | 0   | 0     | 0      | 0 | 0  | 0            | 0    | 0    | 0   | 0    | 0  | 1 |

| DOMO             | 2       | 0  | 0  | 0   | 0   | 0   | 0     | 0      | 0 | 0  | 0            | 0    | 0    | 0   | 0    | 1  | 0 |

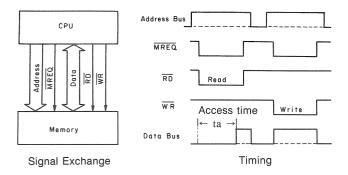

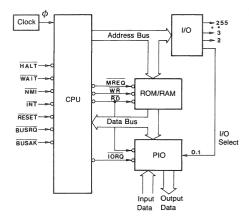

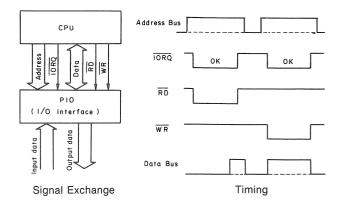

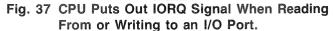

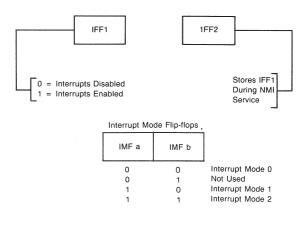

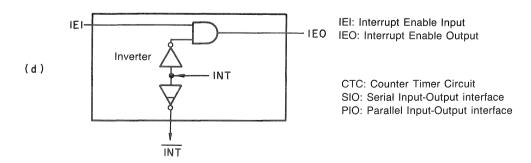

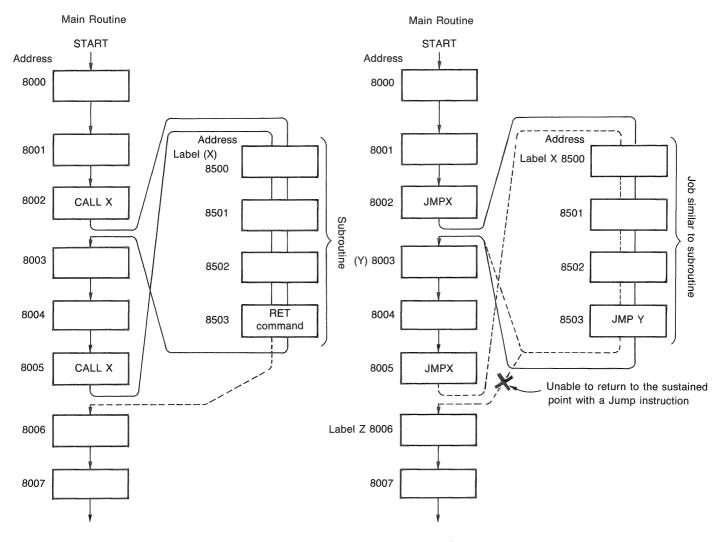

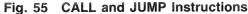

| ROM 0            | 3       | 0  | 0  | 0   | 0   | 0   | 0     | 0      | 0 | 0  | 0            | 0    | 0    | 0   | 0    | 1  | 1 |